## Design of Scalable PGAS Collectives for NUMA and Manycore Systems

Damián Álvarez Mallón

Ph.D. in Information Technology Research University of A Coruña, Spain

Ph.D. in Information Technology Research University of A Coruña, Spain

DOCTORAL THESIS

# Design of Scalable PGAS Collectives for NUMA and Manycore Systems

Damián Álvarez Mallón

October 2014

PhD Advisor: Guillermo López Taboada

Dr. Guillermo López Taboada Profesor Contratado Doctor Dpto. de Electrónica y Sistemas Universidade da Coruña

#### CERTIFICA

Que la memoria titulada "Design of Scalable PGAS Collectives for NUMA and Manycore Systems" ha sido realizada por D. Damián Álvarez Mallón bajo mi dirección en el Departamento de Electrónica y Sistemas de la Universidade da Coruña (UDC) y concluye la Tesis Doctoral que presenta para optar al grado de Doctor por la Universidade da Coruña con la Mención de Doctor Internacional.

En A Coruña, a Martes 10 de Junio de 2014

Fdo.: Guillermo López Taboada Director de la Tesis Doctoral

A todos/as os/as que me ensinaron algo Polo bo e polo malo

## Acknowledgments

Quoting Isaac Newton, but without comparing me with him: "If I have seen further it is by standing on the shoulders of giants". Specifically, one of the giants whose shoulder I have found particularly useful is my Ph.D. advisor, Guillermo López Taboada. His support and dedication are major factors behind this work, and it would not exist without them. I cannot forget Ramón Doallo and Juan Touriño, that allowed me become part of the Computer Architecture Group. Thanks to all of them I can call myself a member of the HPC community.

A special place in my acknowledgements is for my colleagues at the Galicia Supercomputing Center (CESGA). With the help of Andrés Gómez, Carlos Mouriño and Juan Pichel I have grow up professionally and gather a considerable amount of knowledge that just experience can provide. I cannot close this part of the acknowledgements without mentioning Brian Wibecan, that kindly hosted me at HP and shared with me his insightful ideas.

Lars Koesterke also has my gratitude. His support made possible the manycore evaluation, and his comments also improved it significantly.

I would like also to thank Wolfgang Gürich. He trusted me more than three years ago with a job at Jülich Supercomputing Centre (JSC). Without him a huge part of this Thesis would not be there, and I owe him much more than that. Thomas Fieseler also supported me during this endeavor, and for that I am grateful.

Of course I am also thankful to Hewlett-Packard S.L. for funding the project "Improving UPC Usability and Performance in Constellation Systems: Implementation/Extension of UPC Libraries", CESGA for kindly providing access to the Finis Terrae, Superdome and SVG systems, in particular the *sysadmins* Carlos, Javier, Pablo and Alex for all their patience, Texas Advance Computing Center (TACC) for the time allocated for the manycore evaluation in the Stampede supercomputer, and JSC for providing access to the JUDGE and JuRoPA clusters.

Last but not least –in fact quite the opposite–, I want to express my gratitude to my family. Their lessons are the most valuable that anybody can learn, and go well beyond what words can express.

Damián Álvarez Mallón

Both optimists and pessimists contribute to our society. The optimist invents the airplane and the pessimist the parachute. Gil Stern

## Resumo

O número de núcleos por procesador está crecendo, convertindo aos sistemas multinúcleo en omnipresentes. Isto implica lidiar con múltiples niveis de memoria en sistemas NUMA, accesibles a través de complexas xerarquías para procesar as crecentes cantidades de datos. A clave para un movemento eficiente e escalable de datos é o uso de operacións de comunicación colectivas que minimizen o impacto dos colos de botella. Usar comunicacións unilaterais vólvese máis importante nestes sistemas, para evitar sincronizacións entre pares de procesos en operacións colectivas implementadas usando funcións punto a punto bilaterais. Esta tese propón unha serie de algoritmos que proporcionan bo rendemento e escalabilidade en operacións colectivas. Estes algoritmos usan árbores xerárquicas, solapamento de comunicacións unilaterais, pipelining de mensaxes e afinidade NUMA. Desenvolveuse unha implementación para UPC, unha linguaxe PGAS cuxo rendemento tamén foi avaliado nesta tese. Para comprobar o rendemento destes algoritmos unha nova ferramenta de microbenchmarking foi deseñada e implementada. A avaliación dos algoritmos, realizada en 6 sistemas representativos, con 5 arquitecturas de procesador e 5 redes de interconexión diferentes, mostrou en xeral un bo rendemento e escalabilidade, mellor que os algoritmos líderes en MPI en moitos casos, o que confirma o potencial dos algoritmos desenvoltos para arquitecturas multi- e manycore.

## Resumen

El número de núcleos por procesador está creciendo, convirtiendo a los sistemas multinúcleo en omnipresentes. Esto implica lidiar con múltiples niveles de memoria en sistemas NUMA, accesibles a través de complejas jerarquías para procesar las crecientes cantidades de datos. La clave para un movimiento eficiente y escalable de datos es el uso de operaciones de comunicación colectivas que minimizen el impacto de los cuellos de botella. Usar comunicaciones unilaterales se vuelve más importante en estos sistemas, para evitar sincronizaciones entre pares de procesos en operaciones colectivas implementadas usando funciones punto a punto bilaterales. Esta tesis propone una serie de algoritmos que proporcionan buen rendimiento y escalabilidad en operaciones colectivas. Estos algoritmos usan árboles jerárquicos, solapamento de comunicaciones unilaterais, pipelining de mensajes y afinidad NU-MA. Se ha desarrollado una implementación para UPC, un lenguaje PGAS cuyo rendimiento también ha sido evaluado en esta tesis. Para comprobar el rendimiento de estos algoritmos una nueva herramienta de microbenchmarking fue diseñada e implementada. La evaluación de los algoritmos, realizada en 6 sistemas representativos, con 5 arquitecturas de procesador y 5 redes de interconexión diferentes, ha mostrado en general un buen rendimiento y escalabilidad, mejor que los algoritmos líderes en MPI en muchos casos, lo que confirma el potencial de los algoritmos desarrollados para arquitecturas multi- y *manycore*.

## Abstract

The increasing number of cores per processor is turning multicore-based systems in pervasive. This involves dealing with multiple levels of memory in NUMA systems, accessible via complex interconnects in order to dispatch the increasing amount of data required. The key for efficient and scalable provision of data is the use of collective communication operations that minimize the impact of bottlenecks. Leveraging one-sided communications becomes more important in these systems, to avoid synchronization between pairs of processes in collective operations implemented using two-sided point to point functions. This Thesis proposes a series of collective algorithms that provide a good performance and scalability. They use hierarchical trees, overlapping one-sided communications, message pipelining and NUMA binding. An implementation has been developed for UPC, a PGAS language whose performance has been also assessed in this Thesis. In order to assess the performance of these algorithms a new microbenchmarking tool has been designed and implemented. The performance evaluation of the algorithms, conducted on 6 representative systems, with 5 different processor architectures and 5 different interconnect technologies, has shown generally good performance and scalability, outperforming leading MPI algorithms in many cases, which confirms the suitability of the developed algorithms for multi- and manycore architectures.

## Publications from the Thesis

#### Journal Papers (3 accepted + 1 submitted)

- Damián A. Mallón, Guillermo L. Taboada and Lars Koesterke MPI and UPC Broadcast, Scatter and Gather Algorithms in Xeon Phi. Submitted to *Journal* of Parallel Computing, 2014

- Damián A. Mallón, Guillermo L. Taboada, Carlos Teijeiro, Jorge González-Domínguez, Andrés Gómez and Brian Wibecan Scalable PGAS Collective Operations in NUMA Clusters. In *Journal of Cluster Computing*, pages 1–23, 2014. Pending publication.

- Carlos Teijeiro, Guillermo L. Taboada, Juan Touriño, , Ramón Doallo, Damián A. Mallón, J. Carlos Mouriño, and Brian Wibecan. Design and Implementation of an Extended Collectives Library for Unified Parallel C. In *Journal of Computer Science and Technology*, volume 28, number 1, pages 72–89, 2012.

- Jorge González-Domínguez, María J. Martín, Guillermo L. Taboada, Juan Touriño, Ramón Doallo, Damián A. Mallón, and Brian Wibecan. UPCBLAS: A Library for Parallel Matrix Computations in Unified Parallel C. In *Journal of Concurrency and Computation: Practice and Experience*, volume 24, number 14, pages 1645–1667, 2012.

### International Conferences (6)

- Jorge González-Domínguez, María J. Martín, Guillermo L. Taboada, Juan Touriño, Ramón Doallo, Damián A. Mallón, and Brian Wibecan. A Library for Parallel Numerical Computation in UPC. Poster in *The 24th Conference* on Supercomputing (SC'11), Seattle, WA, (USA), 2011.

- Damián A. Mallón, J. Carlos Mouriño, Andrés Gómez, Guillermo L. Taboada, Carlos Teijeiro, Juan Touriño, Basilio B. Fraguela, Ramón Doallo, and Brian Wibecan. UPC Operations Microbenchmarking Suite (Research Poster). Poster in *The 25th International Supercomputing Conference (ISC'10)*, Hamburg, Germany, 2010.

- Damián A. Mallón, J. Carlos Mouriño, Andrés Gómez, Guillermo L. Taboada, Carlos Teijeiro, Juan Touriño, Basilio B. Fraguela, Ramón Doallo, and Brian Wibecan. UPC Performance Evaluation on a Multicore System. In Proc. 3rd Conf. on Partitioned Global Address Space Programming Models (PGAS'09), pages 9:1–9:7, Ashburn, VA (USA), 2009.

- Carlos Teijeiro, Guillermo L. Taboada, Juan Touriño, Basilio B. Fraguela, Ramón Doallo, Damián A. Mallón, Andrés Gómez, J. Carlos Mouriño, and Brian Wibecan. Evaluation of UPC Programmability Using Classroom Studies. In Proc. 3rd Conf. on Partitioned Global Address Space Programming Models (PGAS'09), pages 10:1–10:7, Ashburn, VA (USA), 2009.

- Damián A. Mallón, Guillermo L. Taboada, Carlos Teijeiro, Juan Touriño, Basilio B. Fraguela, Andrés Gómez, Ramón Doallo, José Carlos Mouriño Performance Evaluation of MPI, UPC and OpenMP on Multicore Architectures. In *Proc. 16th Euro PVM/MPI (EuroPVM/MPI'09)*, pages 174–184, Espoo, Finland, 2009.

- Guillermo L. Taboada, Carlos Teijeiro, Juan Touriño, Basilio B. Fraguela, Ramón Doallo, José Carlos Mouriño, Damián A. Mallón, and Andrés Gómez. Performance Evaluation of Unified Parallel C Collective Communications. In Proc. 11th IEEE Intl. Conf. on High Performance Computing and Communications (HPCC'09), pages 69-78, Seoul, Korea, 2009.

## Technical Reports (1)

Damián A. Mallón, Andrés Gómez and Guillermo L. Taboada. Performance Evaluation of Finis Terrae. Technical Report CESGA-2009-001, 2009.

## Resumo da Tese

### Introdución

Nos últimos anos a mellora do rendemento dos procesadores tivo un cambio de tendencia. Tradicionalmente, con cada xeración de microprocesadores as aplicacións aumentaban o seu rendemento de forma totalmente transparente, debido ás melloras na microarquitectura e ao aumento de frecuencia. Isto xa non é posible hoxe, e os procesadores aumentan as súas prestacións doutro xeito. Nesta nova era os procesadores incrementan o seu número de núcleos. Ca aparición de coprocesadores *manycore* esta tendencia acentúase aínda máis, xa que o rendemento de cada núcleo individualmente non só non incrementa, senón que diminúe. Como efecto colateral deste feito, a presión sobre o subsistema de memoria é máis grande, e precísase maior ancho de banda a memoria. A resposta é a inclusión de varios controladores de memoria por nodo, o que causa que a maior parte dos sistemas de computación de altas prestacións modernos sexan Non-Uniform Memory Access (NUMA). A situación máis habitual é que cada procesador teña o seu propio controlador, aínda que nalgúns casos un único chip pode conter varios controladores de memoria.

Como resultado as aplicacións teñen que adaptarse acordemente. Seguindo a inercia inicial, o modelo de programación máis popular hoxe en día é un híbrido que usa paso de mensaxes (MPI) para comunicación entre procesos que non comparten memoria, e un modelo de fíos con memoria compartida (OpenMP). Porén, ese modelo dificulta a programación das aplicacións, e é proclive a erros. A comunidade de computación de altas prestacións propuxo unha alternativa, denominada Partitioned Global Address Space (PGAS). Neste modelo hai unha parte da memoria que é lóxicamente compartida, aínda que físicamente non o sexa. Deste xeito evítanse os problemas e a complexidade que o modelo de paso de mensaxes trae consigo, e permítense comunicacións unilaterais que non requiren sincronización. No entanto, para obter bo rendemento cómpre ter unha boa localidade de datos, xa que acceder á memoria remota constantemente resultaría nun mal rendemento.

En todo modelo de programación que inclúa memoria distribuída a algún nivel é necesario ter primitivas eficientes de redistribución de datos. Estas primitivas son operacións colectivas executadas por todos os procesos que participan na devandita operación. A maioría das aplicacións usan estas operacións colectivas nalgún punto da súa execución. Por tanto, a escalabilidade e rendemento destas operacións xoga un papel moi importante para permitir mellores tempos de execución en situacións con decenas de miles de núcleos.

A confluencia de todos estes factores –novas arquitecturas de procesadores con moitos máis núcleos que as tradicionais e xerarquías de memoria máis profundas, novos modelos de programación, e a necesidade de operacións de redistribución de datos eficientes e escalables– é a motivación desta tese de doutoramento, titulada "Design of Scalable PGAS Collectives for NUMA and Manycore Systems". O traballo focalizouse en Unified Parallel C (UPC), unha linguaxe PGAS baseada en C, e unha das alternativas PGAS máis coñecidas. Co fin de probar o potencial de UPC para a computación de altas prestacións nesta tese se realizou unha avaliación de rendemento desta linguaxe, co compilador e runtime de UPC máis popular (Berkeley UPC). Adicionalmente, co obxetivo de avaliar o rendemento dos algoritmos propostos, desenvolveuse unha ferramenta de medición de rendemento, que constitúe a primera do seu xénero en UPC. O último paso foron avaliacións de rendemento dos algoritmos en múltiples contornas, empregando 5 sistemas NUMA e 1 sistema *manycore*.

#### Metodoloxía de Traballo

A metodoloxía de traballo desta tese consta dunha serie de tarefas para realizar. Tales tareas deberán:

• Ter en conta o estado da arte e os recursos cos que se contan.

- Ser organizadas en certa orde lóxica.

- Ter unha duración determinada.

- Formar bloques de traballo relacionados, de forma que cada bloque represente unha etapa claramente distinguible.

- Ter unha serie de metas por bloque que determinan o éxito da tese.

Ademais, dada a rápida evolución da computación de altas prestacións, novas tarefas pódense levar a cabo se os recursos dispoñibles o permiten e os resultados obtidos teñen un impacto significativo. Deste xeito, a listaxe de tarefas (Tn), agrupadas en bloques (Bn), desenvolvidas na presente tese foron:

- **B1** Estudo do estado da arte en modelos de programación e algoritmos de operacións colectivas.

- T1.1 Estudo de alternativas actuais para programación paralela, incluíndo modelos de programación para sistemas de memoria distribuída e memoria compartida.

- T1.2 Familiarización coas linguaxes existentes que foron estendidas para soportar características PGAS, linguaxes creadas especificamente, e outras alternativas PGAS baseadas en bibliotecas.

- T1.3 Estudo de características relevantes da linguaxe UPC, con atención ás características útiles desde o punto de vista de deseño de operacións co-lectivas.

- T1.4Estudo en profundidade de algoritmos para operacións colectivas na literatura, con especial atención ao estado da arte á referencia en HPC, MPI.

- **B2** Estudo de rendemento de UPC.

- T2.1 Busca de ferramentas de avaliación de rendemento que permitan comparación entre MPI –por ser a alternativa de programación paralela máis popular– e UPC.

- T2.2 Avaliación de rendemento de UPC cos devanditos *benchmarks*, incluíndo unha análise comparativa con MPI.

- T2.3 Análise doutros traballos de avaliación de rendemento de UPC, con especial atención ás súas conclusións sobre o posible futuro de UPC.

- B3 Deseño e implementación dunha ferramenta de medición de rendemento.

- T3.1 Estudo de alternativas de microbenchmarking para MPI e OpenMP en distintos eidos, en particular no tocante a comunicacións e operacións colectivas.

- T3.2 Deseño dunha ferramenta de *microbenchmarking* de comunicacións en UPC, que resulte familiar a outros usuarios con experiencia en MPI e que permita realizar estudos comparativos.

- T3.3 Implementación da primera ferramenta de *microbenchmarking* de comunicacións en UPC.

- **B4** Deseño e implementación de algoritmos para operacións colectivas para arquitecturas NUMA e multicore.

- T4.1 Deseño dun algoritmo xeral que sirva de base para varias operacións colectivas, baseado nunha estructura de árbore, e que aproveite as operacións unilaterais de UPC.

- T4.2 Exploración do espazo de posibles optimizacións do algoritmo xeral, incluíndo solapamento de comunicacións, distintas formas de árbore, e técnicas para obter escalabilidade con miles de núcleos.

- T4.3 Refinamento e adaptación do algoritmo para as operacións que así o requiran debido as súas particularidades, no tocante á distribución de datos e operacións relacionadas.

- T4.4 Implementación da familia de algoritmos na súa forma básica, para usar como orixe das versións optimizadas.

- T4.5 Implementación usando os algoritmos base das optimizacións deseñadas de forma incremental.

- T4.6 Estudo de optimizacións extra para funcións que non encaixen no algoritmo xeral debido aos movementos de datos necesarios.

- T4.7 Implementación das optimizacións para ditas funcións.

- B5 Análise de rendemento dos algoritmos implementados en arquitecturas NUMA.

- T5.1 Avaliación de rendemento dos algoritmos baseados en árbores en múltiples sistemas NUMA con diferentes características –procesadores, interconexión intranodo e interconexión internodo–.

- T5.2 Análise comparativa con outras alternativas en UPC, en particular a implementación de referencia e a implementación do *runtime* con máis rendemento dispoñible.

- $T5.3\,$  Análise comparativa co estado do arte en MPI en experimentos a grande escala con miles de núcleos.

- T5.4 Análise da contribución de cada técnica de optimización ao rendemento final de cada variación das operacións colectivas.

- **B6** Análise de rendemento dos algoritmos implementados en arquitecturas *many*core.

- T6.1 Avaliación de rendemento dos algoritmos baseados en árbores en sistemas manycore, escalando os experimentos ata a orde de decenas de miles de núcleos.

- T6.2 Análise comparativa co estado da arte en MPI en ditos sistemas, incluíndo runtimes especialmente adaptados e optimizados para dita arquitectura.

- T6.3 Análise comparativa do rendemento das colectivas en UPC e MPI en procesadores manycore –Intel Xeon Phi– contra o rendemento obtido en procesadores multicore.

- B7 Extracción de conclusións.

- T7.1 Resumo do traballo e extracción de conclusións.

- T7.2 Análise de traballo futuro e liñas abertas.

- $T7.3\,$ Escritura da memoria da tese de doutoramento.

A presente memoria recolle o traballo feito en cada tarea. Cada capítulo contén exactamente un bloque dos anteriormente enumerados.

Cada bloque ten unha serie de metas que se queren alcanzar. A listaxe de metas (Mn) asociadas con cada bloque (Bn) da tese de doutoramento foi:

- **B1** Estudo do estado da arte en modelos de programación e algoritmos de operacións colectivas.

- M1.1 Obtención de perspectiva en canto a opcións dispoñibles para programación paralela de hardware moderno.

- M1.2 Obtención de ideas para o deseño e implementación de operacións colectivas escalables ata miles de núcleos.

- B2 Estudo de rendemento de UPC.

- M2.1 Determinación da validez de UPC como alternativa para programación de sistemas paralelos para aplicacións científicas.

- B3 Deseño e implementación dunha ferramenta de medición de rendemento.

- M3.1 Proporcionar á comunidade da primeira ferramenta de *microbenchmar*king de comunicacións para UPC.

- **B4** Deseño e implementación de algoritmos para operacións colectivas para arquitecturas NUMA e multicore.

- M4.1 Conxunto de rutinas de operacións colectivas en UPC altamente optimizadas e escalables a sistemas con decenas de miles de núcleos e múltiples rexións NUMA por nodo.

- B5 Análise de rendemento dos algoritmos implementados en arquitecturas NUMA.

- M5.1 Comprensión do rendemento e escalabilidade das operacións optimizadas comparativamente co estado da arte actual en UPC, en sistemas NUMA.

- M5.2 Comprensión do rendemento e escalabilidade das operacións optimizadas comparativamente co estado da arte actual en MPI, en sistemas NUMA.

- M5.3 Comprensión do impacto no rendemento e escalabilidade das distintas técnicas de optimización implementadas.

- **B6** Análise de rendemento dos algoritmos implementados en arquitecturas *many*core.

- M6.1 Comprensión do rendemento e escalabilidade das operacións optimizadas comparativamente co estado da arte actual en MPI, en sistemas many-core.

- M6.2 Comprensión do impacto de cambios profundos na arquitectura de procesadores no rendemento e escalabilidade de operacións colectivas.

- B7 Extracción de conclusións.

- M7.1 Memoria da tese de doutoramento, coa descrición dos pasos realizados e as conclusións obtidas, así como as futuras liñas de traballo.

Os medios necesarios para realizar esta tese de doutoramento, seguindo a metodoloxía de traballo anteriormente descrita, foron os seguintes:

- Proxecto de investigación con financiamento privado e de ámbito internacional: "Improving UPC Usability and Performance in Constellations Systems: Implementation/Extension of UPC Libraries". Financiado por Hewlett-Packard S.L., en colaboración coa Universidade da Coruña, a Universidade de Santiago de Compostela e o Centro de Supercomputación de Galicia.

- Clústers utilizados durante o desenvolvemento e avaliación de rendemento dos algoritmos desta tese:

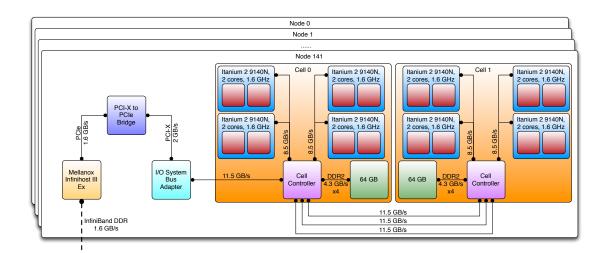

- Supercomputador Finis Terrae (Centro de Supercomputación de Galicia, 2008-2011): 142 nodos con 8 procesadores Intel Itanium 2 dual core, a 1.6 GHz e 128 GB de RAM. A rede de interconexión deste supercomputador é InfiniBand 4x DDR.

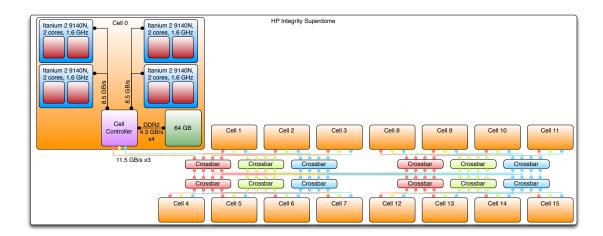

- Nodo Superdome (Centro de Supercomputación de Galicia, 2008-2011): Nodo de cómputo con 64 procesadores Intel Itanium 2 dual core, a 1.6 GHz e 1 TB de RAM.

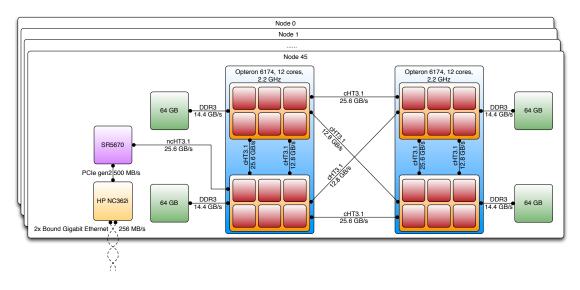

- Supercomputador Virtual Galego 2011 (SVG 2011) (Centro de Supercomputación de Galicia, 2011): 46 nodos con 2 procesadores AMD Opteron, cada un con 12 cores, a 2.2 GHz e 64 GB de RAM. A rede de interconexión é Gigabit Ethernet.

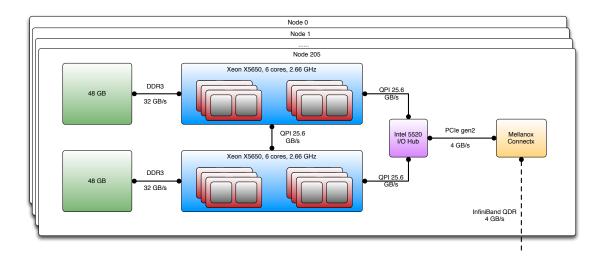

- *JUDGE* (Forschungzentrum Jülich, 2011-actualidade): 206 nodos con 2 procesadores Intel Xeon hexa core, a 2.66 GHz e 96 GB de RAM. A rede de interconexión é InfiniBand 4x QDR.

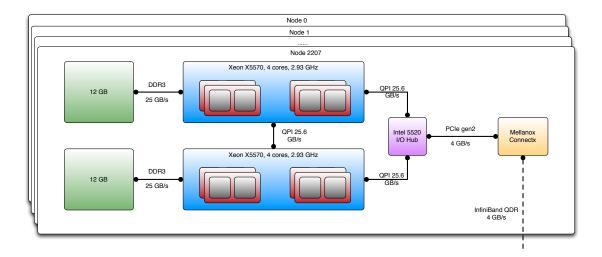

- *JuRoPA* (Forschungzentrum Jülich, 2011-actualidade): 2208 nodos con 2 procesadores Intel Xeon quad core, a 2.93 GHz e 24 GB de RAM. A rede de interconexión é InfiniBand 4x QDR.

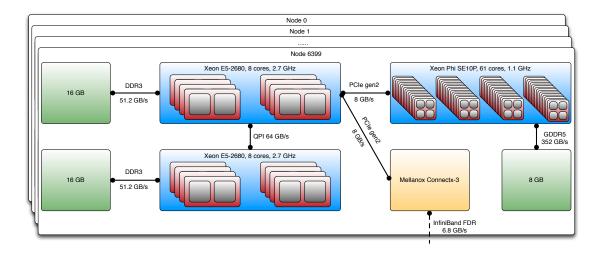

- Stampede (Texas Advanced Computing Center, 2013-actualidade): 6400 nodos con 2 procesadores Intel Xeon octo core, a 2.7 GHz e 32 GB de RAM. Cada nodo conta, ademais, con 1 coprocesador Intel Xeon Phi con 61 cores a 1.1 GHz e 8 GB de RAM. A rede de interconexión é InfiniBand 4x FDR.

- Contrato con Forschungszentrum Jülich GmbH, que excede no momento de escribir esta Tese os 3 anos. Dito contrato posibilitou a realización das tarefas incluídas nos Bloques 5 e 6.

#### Conclusións

Esta tese de doutoramento, "Design of Scalable PGAS Collectives for NUMA and Manycore Systems", demostrou o potencial do modelo PGAS para a implementación de operacións colectivas eficientes e altamente escalables, chegando en moitos casos a render mellor que as actuais solucións neste eido, en moitos escenarios diferentes. A programación de sistemas cada vez máis complexos, con memoria distribuída e compartida, con distintas latencias de acceso a memoria dependendo de que dirección se esté accedendo, e cun hardware evolucionando a alta velocidade, é altamente complicada. O modelo PGAS propón unha alternativa ao tradicional modelo de paso de mensaxes, con algunhas características que evitan en certa medida custosas sincronizacións, e que se poden aplicar ao deseño de bibliotecas de comunicacións. Os programadores de aplicacións científicas usadas en sistemas de altas prestacións recorren con frecuencia a operacións colectivas incluídas nos *runtimes* correspondentes. Como consecuencia, os enxeñeiros de computadores levan anos optimizando e adaptando tales operacións a distintas arquitecturas, dando como resultado unha extensa traxectoria de investigación e historial de algoritmos. A pesar desta traxectoria, o traballo que explora a optimización das ditas operacións usando o modelo PGAS é escaso.

Esta tese analizou o rendemento de UPC en *benchmarks* científicos, concluíndo que é comparable ao rendemento doutras aplicacións baseadas en C e que usan paso de mensaxes como método de comunicación. Porén, e a pesar da boa escalabilidade nalgúns casos, tamén se achou que cómpre prestar atención á optimización do acceso a rede, que nalgúns casos causa unha perda de rendemento usando multiples núcleos. Isto sinala a importancia de optimizar as operacións de comunicacións. En particular, as operacións colectivas teñen especial importancia, debido a súa popularidade e uso frecuente.

No tocante ao deseño de colectivas, esta tese non podía efectuar un traballo metódico e exhaustivo sen contar con ferramentas para medir o rendemento das ditas operacións. Ante a ausencia de ferramentas axeitadas deseñouse e implementouse a primeira ferramenta de *microbenchmarking* para UPC, usando o coñecemento e experiencia obtidos durante anos por científicos, usando paso de mensaxes. Con esta ferramenta fundamental implementada, a avaliación de rendemento en colectivas xa é posible.

No núcleo desta tese está o deseño de algoritmos altamente escalables para operacións colectivas en arquitecturas modernas de supercomputación. Tales algoritmos, implementados en UPC, apoianse nas seguintas técnicas para obter un alto rendemento e escalabilidade:

- Uso de operacións de comunicación unilaterais, empuxando ou tirando de datos

-é dicir, a orixe da operación está no proceso que ten ou necesita os datos,

respectivamente-, dependendo da natureza da operación.

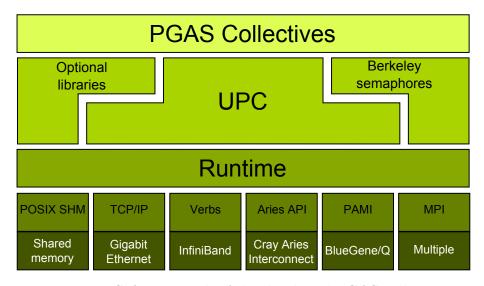

- Uso de árbores cunha estrutura computada na inicialización e reusada durante todo o tempo de execución da aplicación.

- Árbores xerárquicas mapeadas eficientemente no *hardware*, minimizando o uso dos camiños con latencia máis alta e anchos de banda máis pequenos.

- Distinto tipo de árbores no nivel máis baixo, permitindo elixir a forma máis axeitada en cada caso.

- Binding de fíos a rexións NUMA, para asegurar o correcto mapeamento das árbores.

- Dúas técnicas de solapamento de comunicacións, usando tamaños fixos e dinámicos.

As operacións optimizadas avaliáronse exahustivamente en 6 supercomputadores distintos (Stampede, JuRoPA, JUDGE, Finis Terrae, SVG e Superdome), con 5 arquitecturas de procesador distintas (Intel Xeon Phi Many Interconnected Core, Intel Xeon Sandy Bridge, Intel Xeon Nehalem, Intel Itanium 2 e AMD Opteron Magny-Cours), e 5 tecnoloxías de interconexión diferentes (InfiniBand 4x FDR, InfiniBand 4x QDR, InfiniBand 4x DDR, Gigabit Ethernet e Superdome Interconnect). O rendemento e a escalabilidade dos algoritmos deseñados sobrepasa ao das mellores colectivas avaliadas en UPC en case todos os escenarios. As colectivas presentes en implementacións punteiras de *runtimes* MPI tamén se vén sobrepasadas con frecuencia polos algoritmos desta tese, principalmente en escenarios cun alto número de núcleos. Especialmente destacable é o bo rendemento e escalabilidade en sistemas *manycore*, usando máis de 15000 núcleos, a pesar de que o rendemento no tocante a comunicacións nestos sistemas é xeralmente inferior ao obtido en sistemas tradicionais multinúcleo.

#### Principais Contribucións

As principais achegas desta tese son:

• Un estudo de rendemento das operacións colectivas en UPC, previamente aos algoritmos presentados, e materializado en [100].

- Un estudo de rendemento de UPC en *benchmarks* científicos de gran relevancia, e unha análise comparativa con outras opcións populares –MPI e OpenMP–, publicada en [58] e [63].

- A primera ferramenta de *microbenchmarking* para comunicacións en UPC, dispoñible públicamente en [60] e que a día de hoxe acumula máis de 370 descargas. Tal ferramenta foi presentada en [59].

- Unha biblioteca con operacións colectivas altamente optimizadas para arquitecturas modernas usando diversas técnicas.

- Un estudo da devandita biblioteca en 5 sistemas NUMA diferentes (JuRo-PA, JUDGE, Finis Terrae, SVG e Superdome), no que se demostra un gran rendemento, incluso comparado co equivalente ao estado do arte en MPI, e publicado en [62].

- Un estudo dos algoritmos deseñados en un dos sistema manycore máis potentes do mundo neste momento (Stampede), no que os algoritmos desta tese teñen un desempeño que sobrepasa en moitos escenarios ao de algoritmos implementados en runtimes máis optimizados para dito sistema, traballo do que se derivou unha publicación que está sendo considerada para a súa publicación [61].

## Contents

| Pr | reface                                                                    | 1  |

|----|---------------------------------------------------------------------------|----|

| 1. | Background and State-of-the-art in Collective Operations                  | 5  |

|    | 1.1. Programming Models                                                   | 6  |

|    | 1.2. PGAS Programming Model                                               | 7  |

|    | 1.3. Introduction to UPC                                                  | 8  |

|    | 1.4. Collective Operations                                                | 11 |

|    | 1.5. Conclusions of Chapter 1                                             | 14 |

| 2. | Characterization of UPC Performance                                       | 15 |

|    | 2.1. Representative Benchmarks for UPC Performance Characterization .     | 16 |

|    | 2.1.1. NAS Parallel Benchmarks (NPB)                                      | 17 |

|    | 2.1.2. Matrix Multiplication and Stencil Kernels Benchmarks $\ . \ . \ .$ | 22 |

|    | 2.2. Other UPC Performance Studies                                        | 25 |

|    | 2.3. Conclusions of Chapter 2                                             | 26 |

| 3. | UPC Operations Microbenchmarking Suite: UOMS                              | 29 |

|    | 3.1. Benchmarking Suites in HPC                                           | 30 |

|    | 3.2. Design of UPC Operations Microbenchmarking Suite                     | 32 |

|    | 3.3. | UOMS Benchmarking Units                                             | 33  |

|----|------|---------------------------------------------------------------------|-----|

|    | 3.4. | UOMS Options and Compiling Parameters                               | 37  |

|    | 3.5. | Conclusions of Chapter 3                                            | 39  |

| 4. | Des  | ign of Scalable PGAS Collective Algorithms                          | 41  |

|    | 4.1. | UPC Collective Operations                                           | 42  |

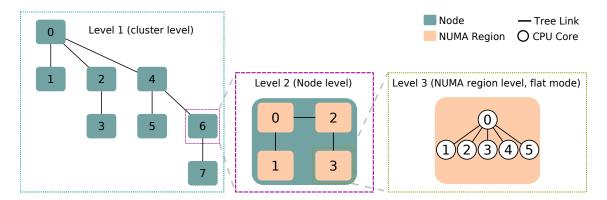

|    |      | 4.1.1. Relocalization Operations                                    | 42  |

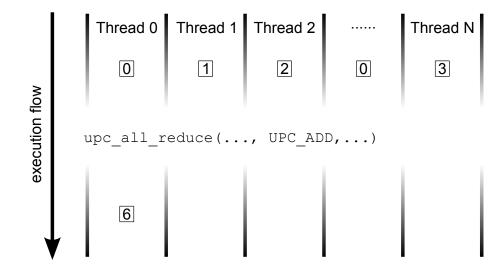

|    |      | 4.1.2. Computational Operations                                     | 45  |

|    |      | 4.1.3. Data Distribution Groups                                     | 47  |

|    | 4.2. | Design of Scalable Collective Operations for PGAS Languages         | 48  |

|    |      | 4.2.1. Broadcast and Baseline Algorithm                             | 49  |

|    |      | 4.2.2. Particularities of Scalable Scatter/Gather Operations        | 57  |

|    |      | 4.2.3. Particularities of Scalable Reduce Operations                | 62  |

|    |      | 4.2.4. Summary of the Implemented Algorithms                        | 66  |

|    |      | 4.2.5. Gather all, Exchange, Permute and Prefix Reduce Optimization | 67  |

|    | 4.3. | Conclusions of Chapter 4                                            | 70  |

| 5. | Per  | f. Evaluation of PGAS Collectives on NUMA Systems                   | 73  |

|    | 5.1. | Experimental Configuration                                          | 73  |

|    | 5.2. | Scalability and Performance of UPC Broadcast                        | 80  |

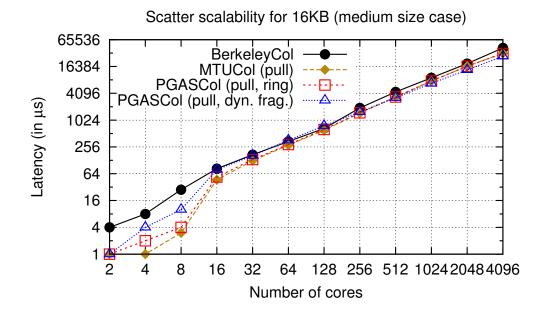

|    | 5.3. | Scalability and Performance of UPC Reduce                           | 85  |

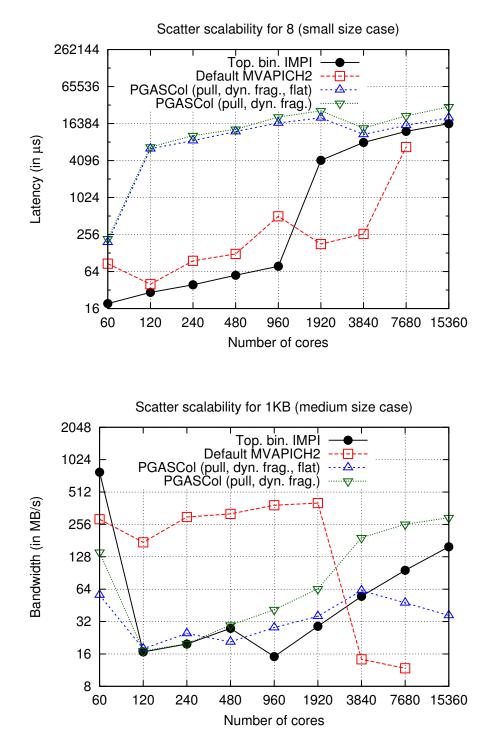

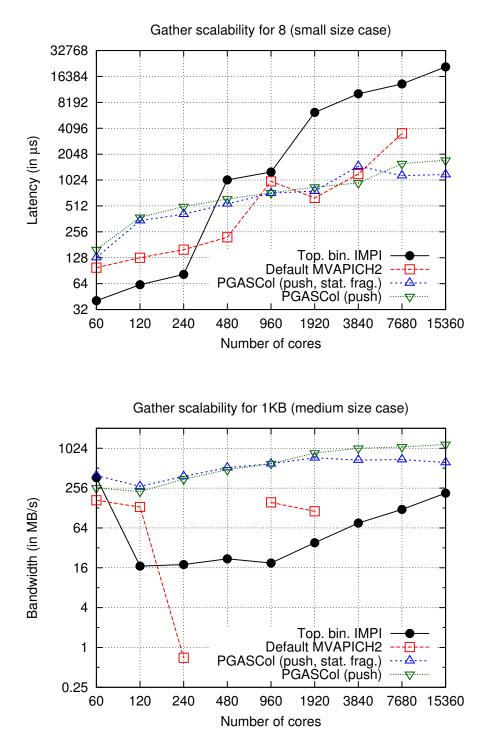

|    | 5.4. | Scalability and Performance of UPC Scatter                          | 94  |

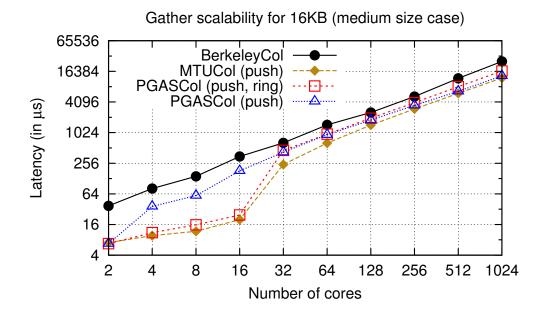

|    | 5.5. | Scalability and Performance of UPC Gather                           | 104 |

|    | 5.6. | Comparative Perf. Analysis of NUMA Algorithms against MPI           | 104 |

|    | 5.7. | Impact on Perf. of Different Optimizations at High Core-Counts 1    | 116 |

|    | 5.8.  | Conclusions of Chapter 5                                                | . 120 |

|----|-------|-------------------------------------------------------------------------|-------|

| 6. | Per   | f. Evaluation of PGAS Collectives on Manycore Systems                   | 123   |

|    | 6.1.  | Algorithms Implemented in Intel MPI and MVAPICH2                        | . 124 |

|    | 6.2.  | Experimental Configuration                                              | . 125 |

|    | 6.3.  | UPC Collective Performance Scalability on Xeon Phi                      | . 128 |

|    | 6.4.  | MPI Collective Performance Scalability on Xeon Phi                      | . 133 |

|    | 6.5.  | Collective Operations Performance on Xeon versus Xeon Phi               | . 138 |

|    | 6.6.  | UPC versus MPI Collective Operations Performance on Xeon Phi            | . 146 |

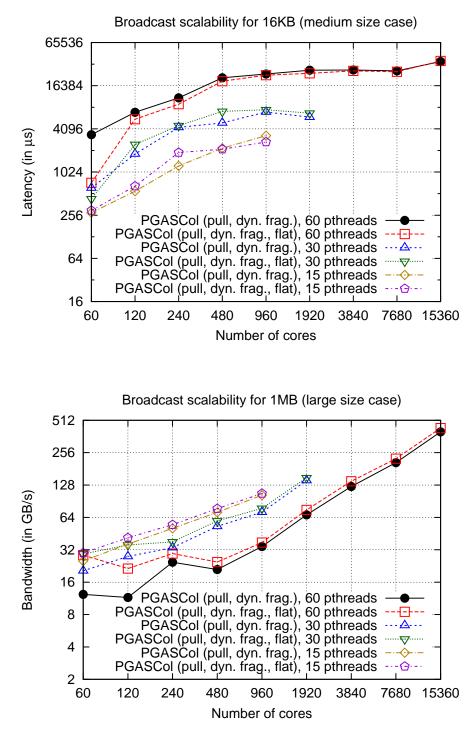

|    | 6.7.  | Impact of Runtime Configuration (pthreads vs. processes) on Xeon<br>Phi | . 150 |

|    | 6.8.  | Conclusions of Chapter 6                                                | . 152 |

| Co | onclu | sions and Future Work                                                   | 153   |

| Re | efere | nces                                                                    | 159   |

| Aj | ppen  | dix: UOMS User Manual                                                   | 177   |

# List of Algorithms

| 1. | Pseudocode of broadcast algorithm with pull approach and message pipelining            | 56 |

|----|----------------------------------------------------------------------------------------|----|

| 2. | Pseudocode of scatter algorithm with pull approach and message pipelin-<br>ing         | 59 |

| 3. | Pseudocode of gather algorithm with push approach and message pipelin-<br>ing (1 of 2) | 60 |

| 4. | Pseudocode of gather algorithm with push approach and message pipelin-<br>ing (2 of 2) | 61 |

| 5. | Pseudocode of scatter algorithm with pull approach on a ring $\ldots$ .                | 63 |

| 6. | Pseudocode of gather algorithm with push approach on a ring                            | 64 |

| 7. | Pseudocode of reduce algorithm with push approach                                      | 65 |

## List of Tables

| 4.1. | Summary of the Optimized PGAS Collective Algorithms Implemented.                                                                  |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|      | Scatter and gather collectives with tree-based algorithms use normal                                                              |    |

|      | binomial trees with binding                                                                                                       | 66 |

|      |                                                                                                                                   |    |

| 5.1. | Bandwidth pull approach algorithm and the pull algorithm with static $% \left( {{{\left[ {{{\rm{B}}_{\rm{B}}} \right]}}} \right)$ |    |

|      | fragmentation and flat trees, in Finis Terrae, Superdome, SVG, JUDGE                                                              |    |

|      | and JuRoPA.                                                                                                                       | 79 |

# List of Figures

| 1.1. | Distribution of arrays in shared memory in UPC                                                | 10 |

|------|-----------------------------------------------------------------------------------------------|----|

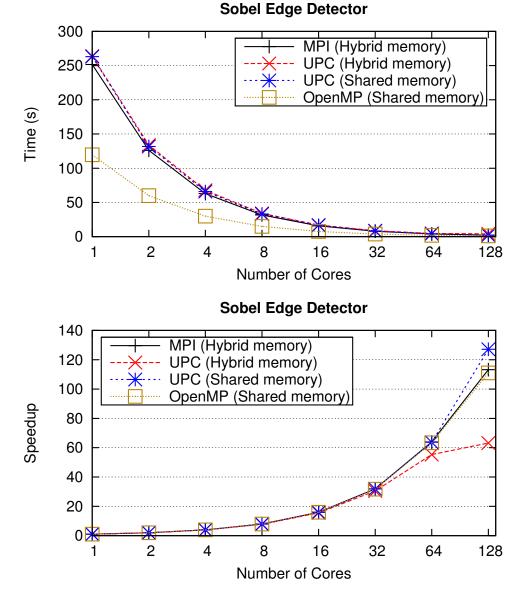

| 2.1. | Performance of NPB kernels on hybrid shared/distributed memory                                | 19 |

| 2.2. | Performance of NPB kernels on shared memory                                                   | 21 |

| 2.3. | Performance of UPC, MPI and OpenMP matrix multiplication im-<br>plementations in Finis Terrae | 23 |

| 2.4. | Performance of UPC, MPI and OpenMP Sobel kernels implementa-<br>tions in Finis Terrae         | 24 |

| 3.1. | Output example of UOMS                                                                        | 36 |

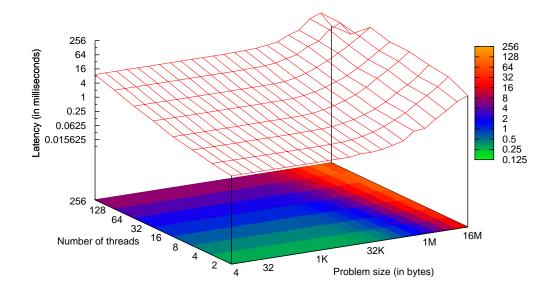

| 3.2. | UPC broadcast latency on Finis Terrae (3D plot example) $\ldots$ .                            | 37 |

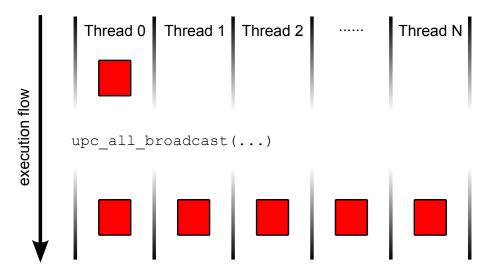

| 4.1. | Broadcast operation in UPC                                                                    | 42 |

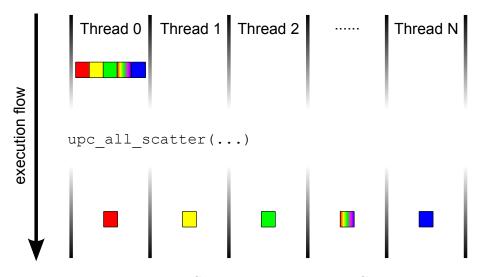

| 4.2. | Scatter operation in UPC                                                                      | 43 |

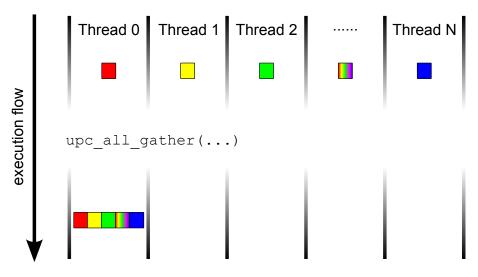

| 4.3. | Gather operation in UPC                                                                       | 44 |

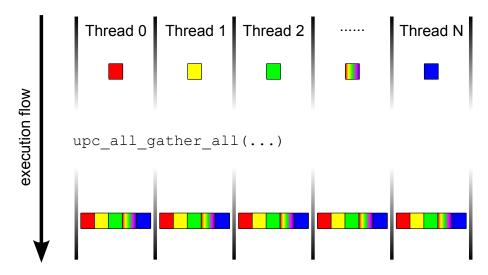

| 4.4. | Gather all operation in UPC                                                                   | 44 |

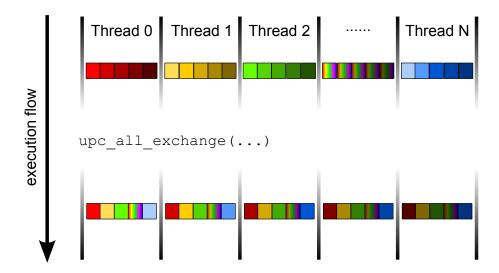

| 4.5. | Exchange operation in UPC                                                                     | 45 |

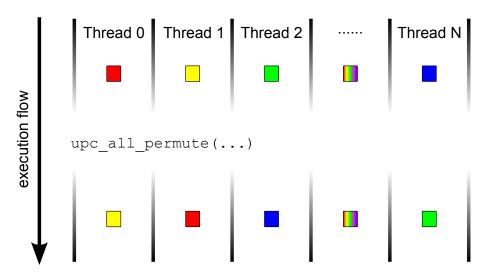

| 4.6. | Permute operation in UPC                                                                      | 46 |

| 4.7. | Reduce operation in UPC                                                                       | 46 |

| 4.8. Prefix reduce operation in UPC                                                            | 47 |

|------------------------------------------------------------------------------------------------|----|

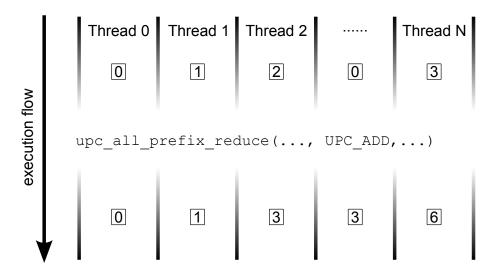

| 4.9. Software stack of the developed PGAS collectives                                          | 49 |

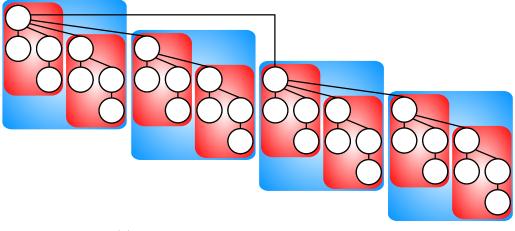

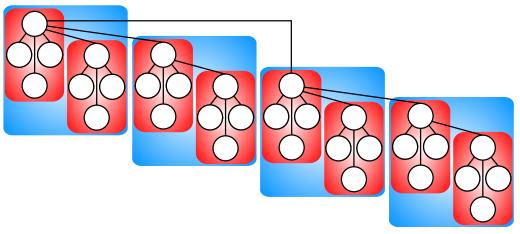

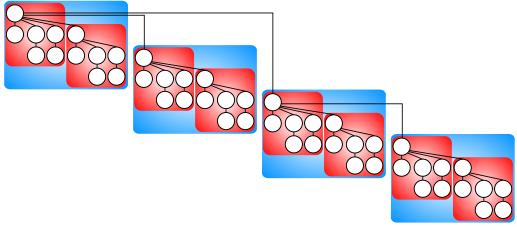

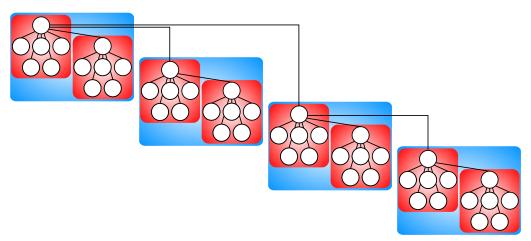

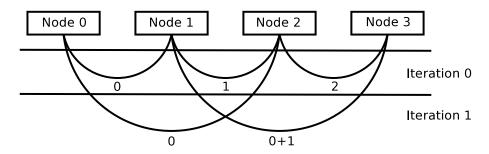

| 4.10. General overview of the scalable algorithm for collective operations<br>on NUMA clusters | 50 |

| 4.11. Tree mapping with a power of 2 number of cores                                           | 54 |

| 4.12. Tree mapping with a non power of 2 number of cores                                       | 55 |

| 4.13. Dissemination barrier algorithm for prefix reduce operation                              | 70 |

| 5.1. Finis Terrae node architecture                                                            | 74 |

| 5.2. Superdome node architecture                                                               | 75 |

| 5.3. SVG 2011 node architecture                                                                | 76 |

| 5.4. JUDGE node architecture                                                                   | 77 |

| 5.5. JuRoPA node architecture                                                                  | 77 |

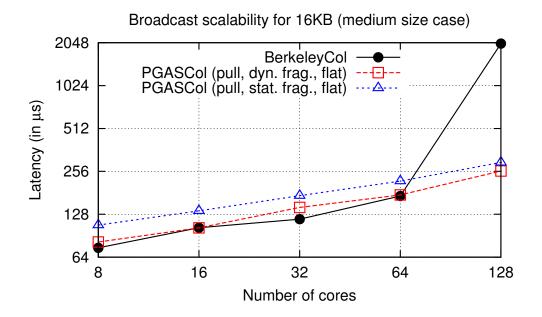

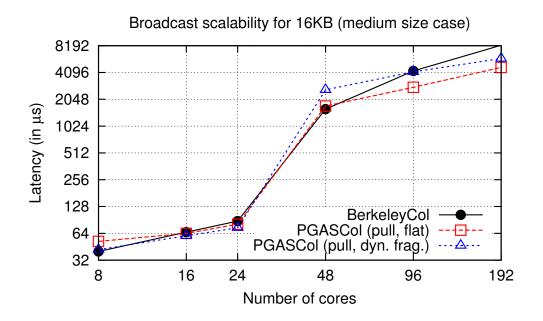

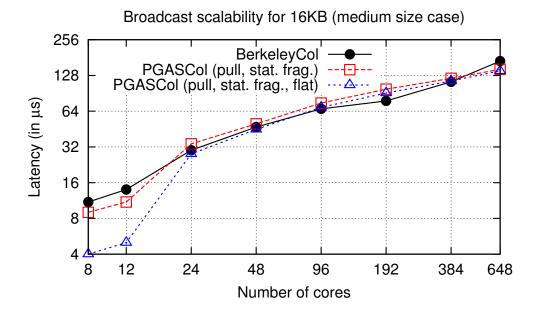

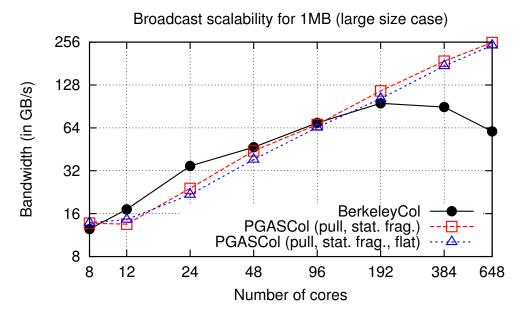

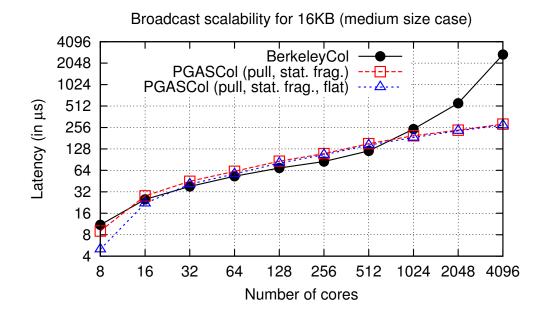

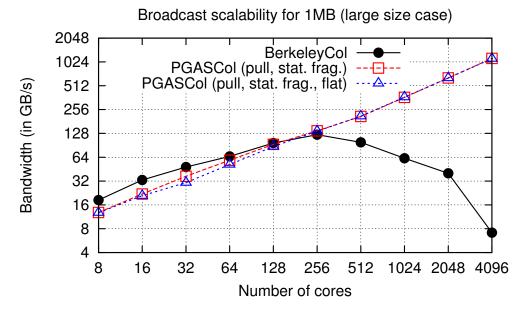

| 5.6. Broadcast performance and scalability on Finis Terrae                                     | 81 |

| 5.7. Broadcast performance and scalability on Superdome                                        | 83 |

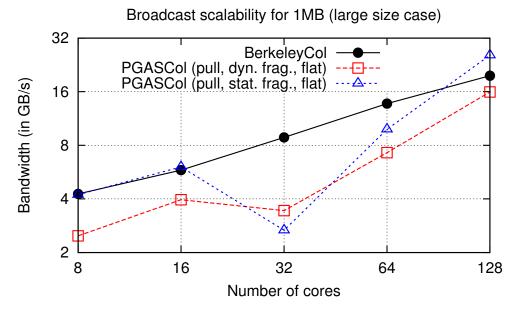

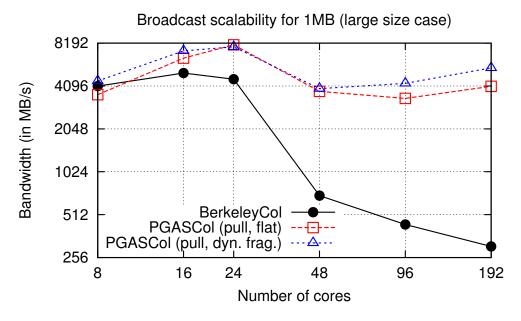

| 5.8. Broadcast performance and scalability on SVG                                              | 84 |

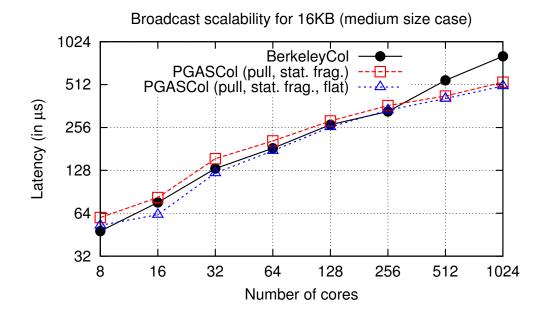

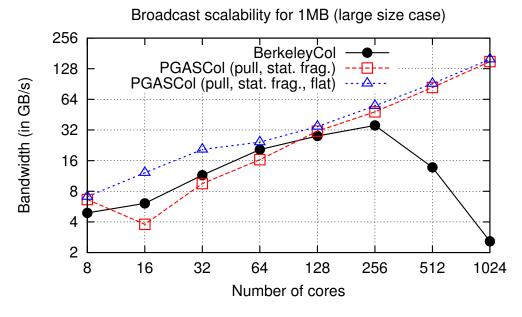

| 5.9. Broadcast performance and scalability on JUDGE                                            | 86 |

| 5.10. Broadcast performance and scalability on JuRoPA                                          | 87 |

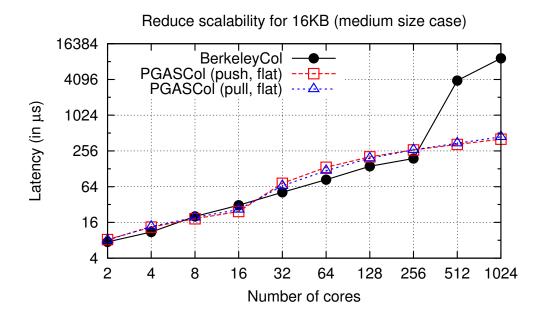

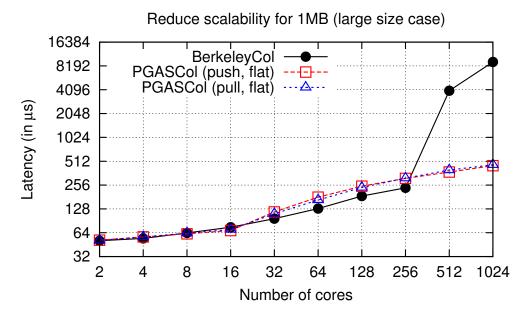

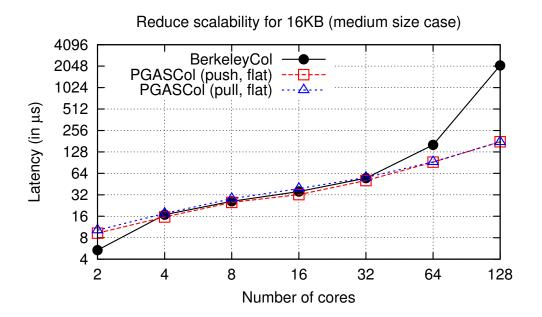

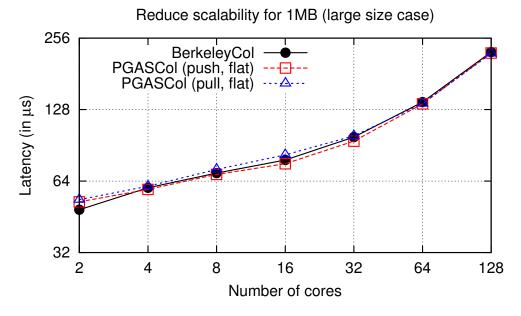

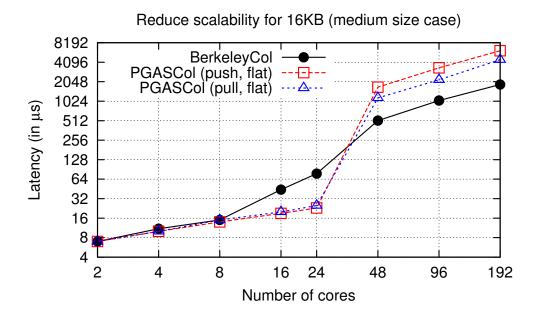

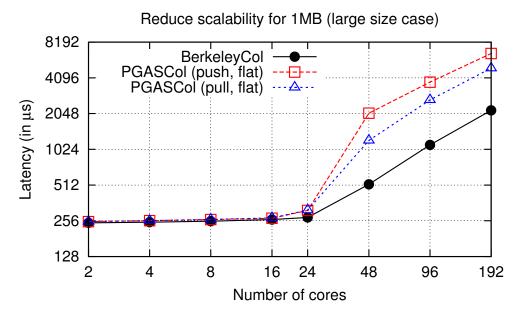

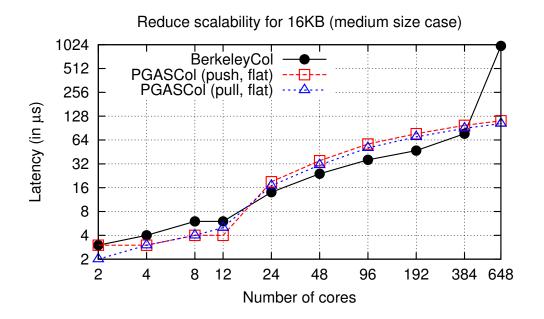

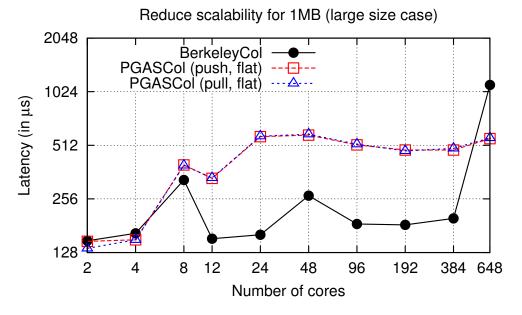

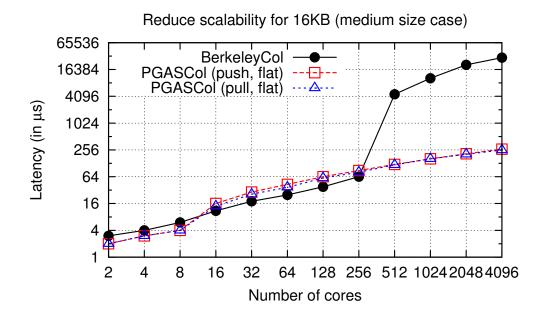

| 5.11. Reduce performance and scalability on Finis Terrae                                       | 89 |

| 5.12. Reduce performance and scalability on Superdome                                          | 90 |

| 5.13. Reduce performance and scalability on SVG                                                | 92 |

| 5.14. Reduce performance and scalability on JUDGE                                              | 93 |

| 5.15. Reduce performance and scalability on JuRoPA                                             | 95 |

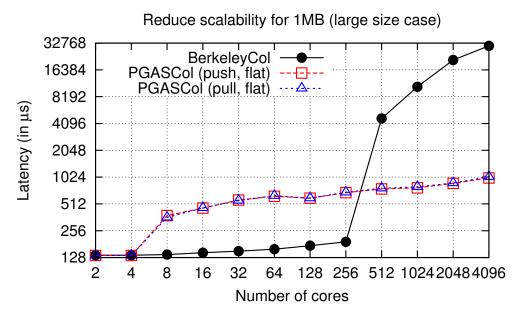

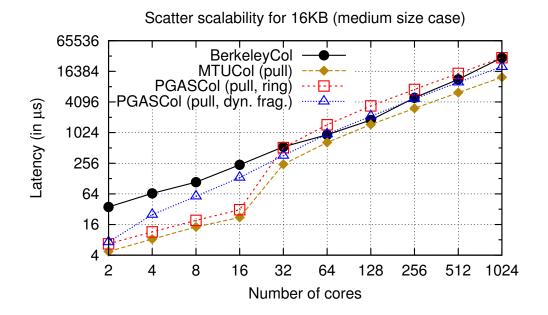

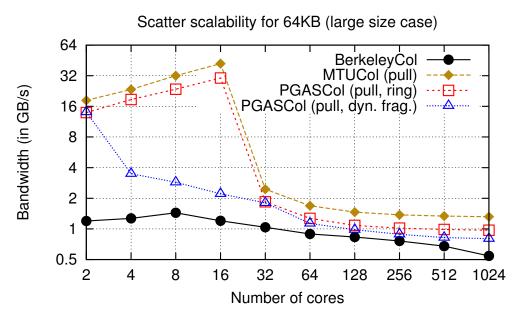

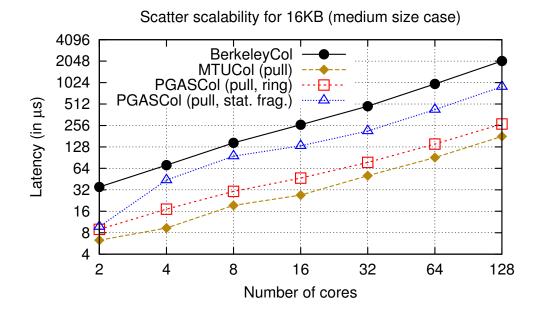

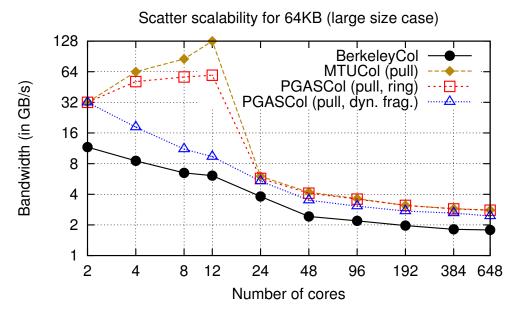

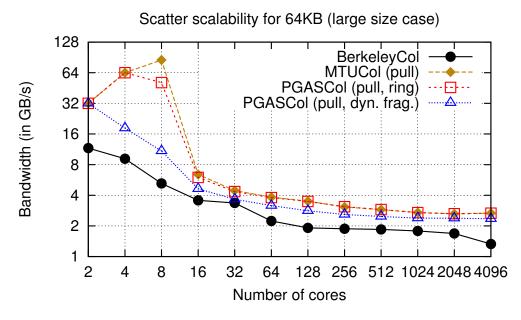

| 5.16. Scatter performance and scalability on Finis Terrae                                      | 97 |

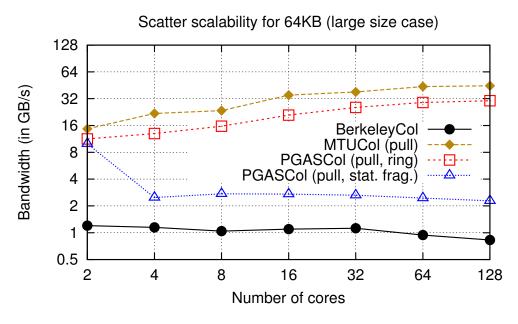

| 5.17. Scatter performance and scalability on Superdome                                         | 99 |

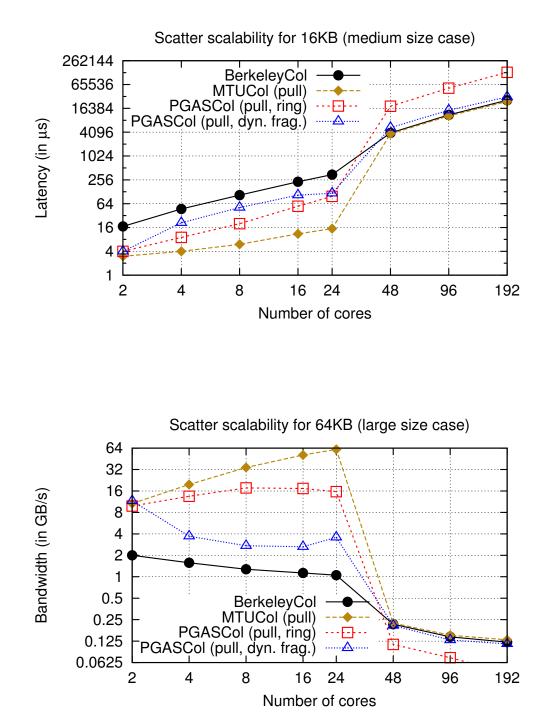

| 5.18. | Scatter performance and scalability on SVG                                            |

|-------|---------------------------------------------------------------------------------------|

| 5.19. | Scatter performance and scalability on JUDGE                                          |

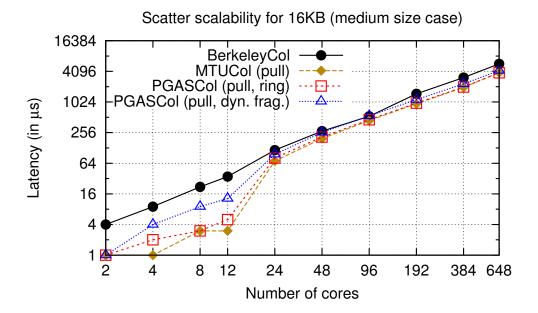

| 5.20. | Scatter performance and scalability on JuRoPA                                         |

| 5.21. | Gather performance and scalability on Finis Terrae                                    |

| 5.22. | Gather performance and scalability on Superdome                                       |

| 5.23. | Gather performance and scalability on SVG                                             |

| 5.24. | Gather performance and scalability on JUDGE                                           |

| 5.25. | Gather performance and scalability on JuRoPA                                          |

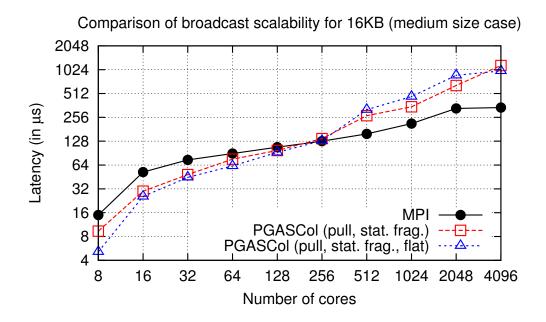

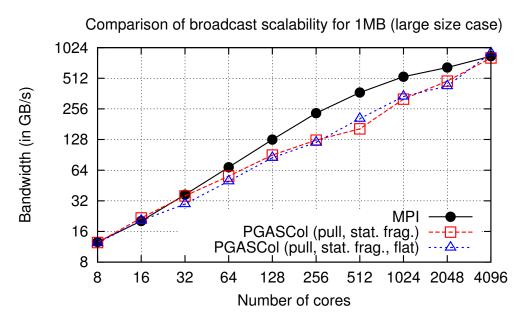

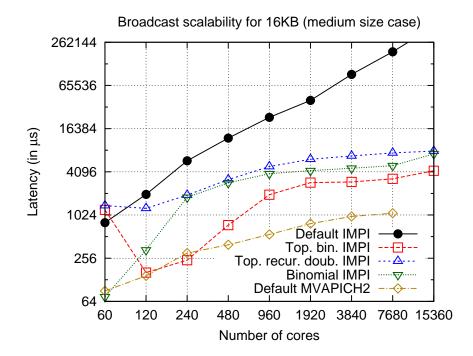

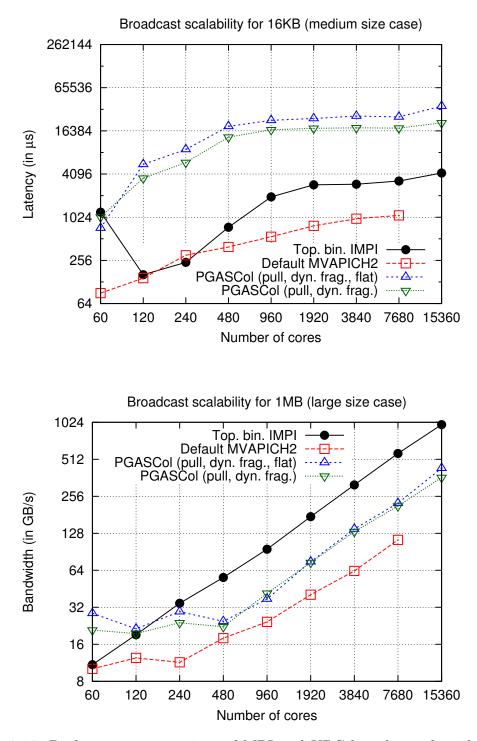

| 5.26. | Comparison of broadcast scalability of NUMA-based algorithms against<br>MPI on JuRoPA |

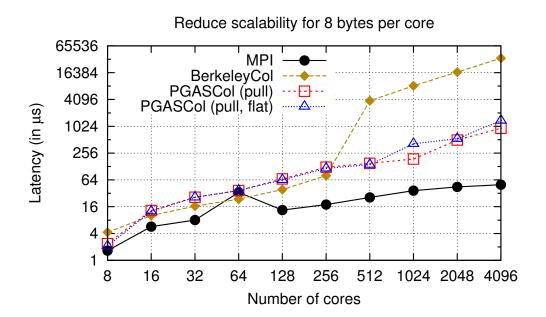

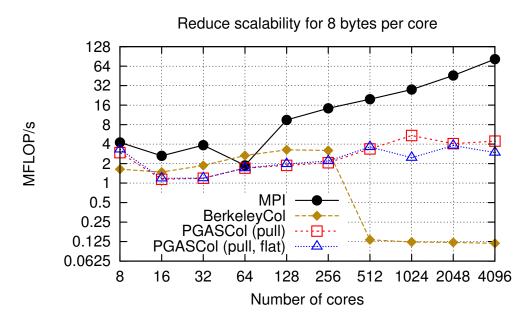

| 5.27. | Comparison of reduce scalability of NUMA-based algorithms against<br>MPI on JuRoPA    |

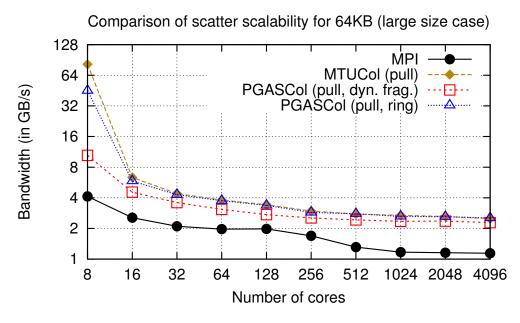

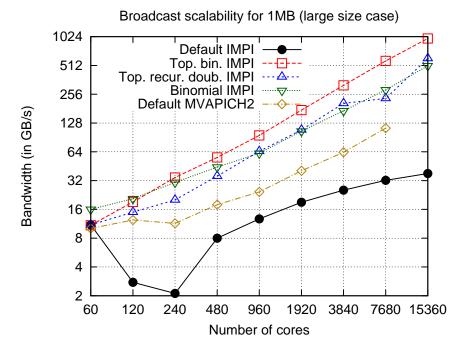

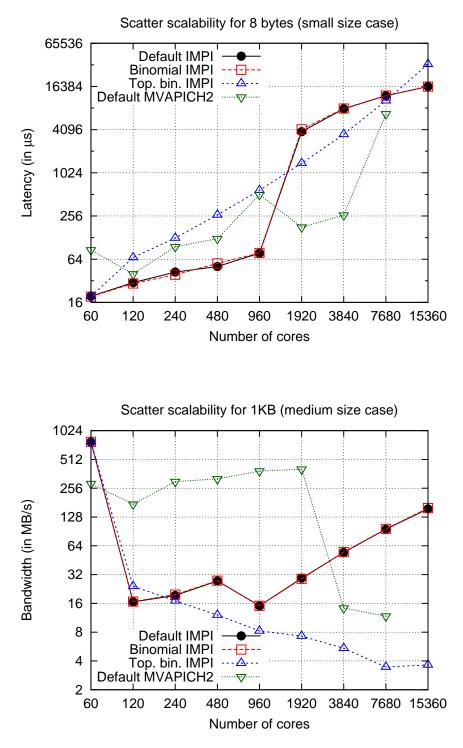

| 5.28. | Comparison of scatter scalability of NUMA-based algorithms against<br>MPI on JuRoPA   |

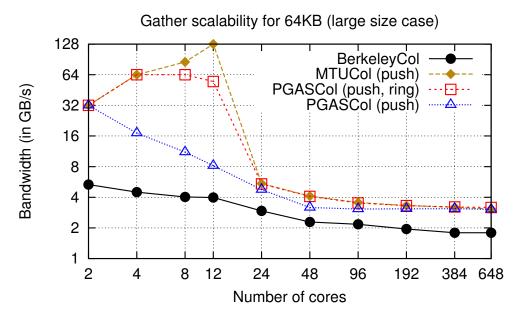

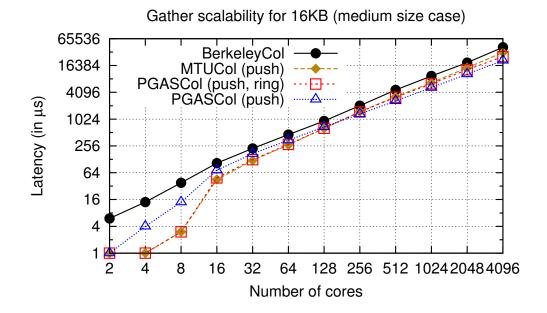

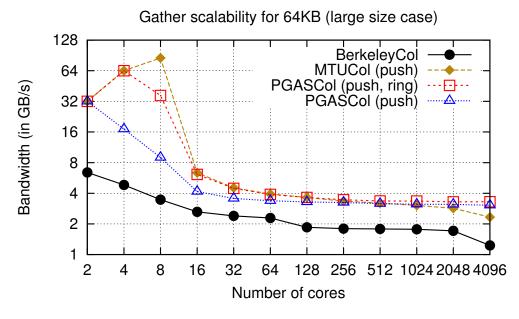

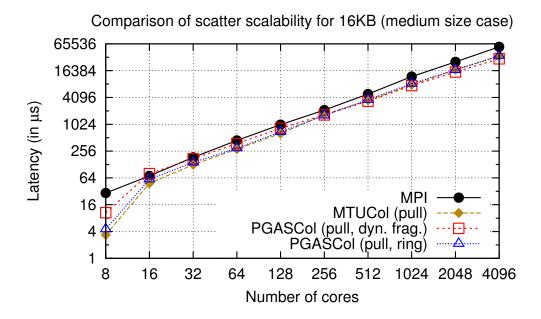

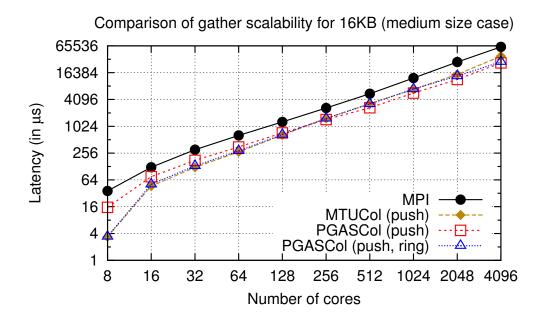

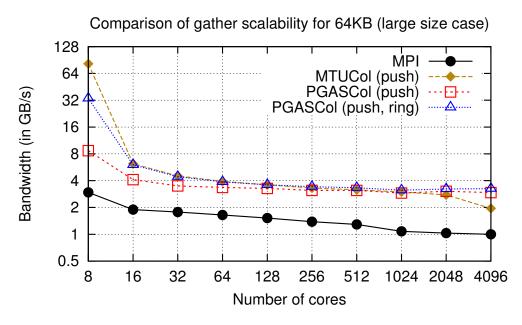

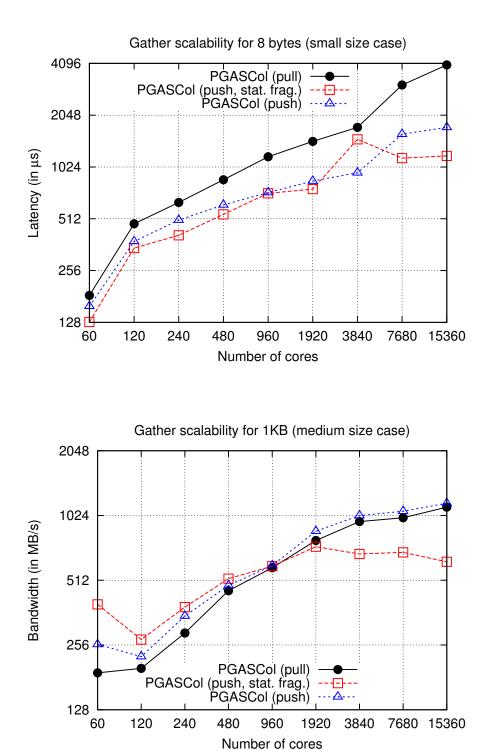

| 5.29. | Comparison of gather scalability of NUMA-based algorithms against<br>MPI on JuRoPA    |

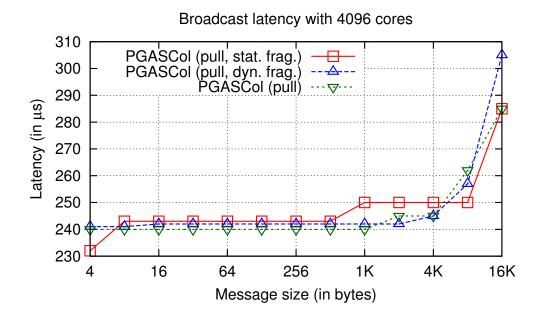

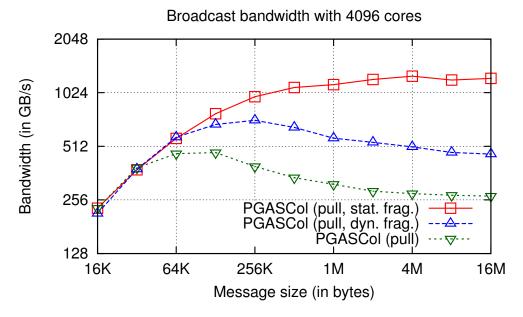

| 5.30. | Impact of message pipelining in broadcast performance                                 |

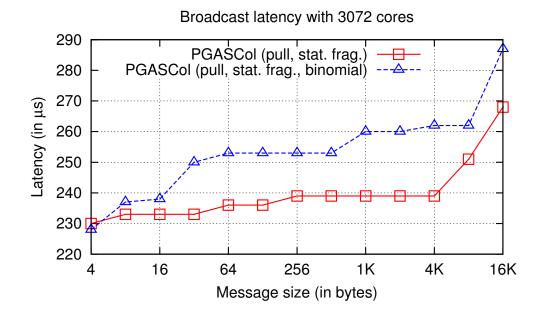

| 5.31. | Impact of multilevel trees in broadcast performance                                   |

| 6.1.  | Stampede node architecture                                                            |

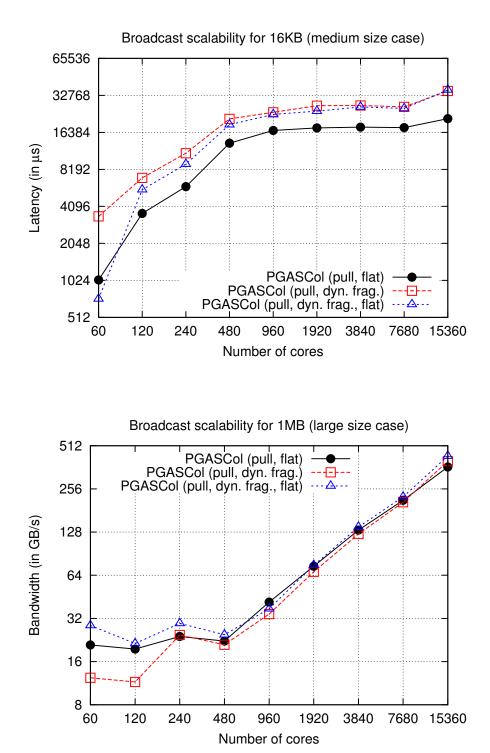

| 6.2.  | UPC broadcast performance and scalability on Xeon Phi 130                             |

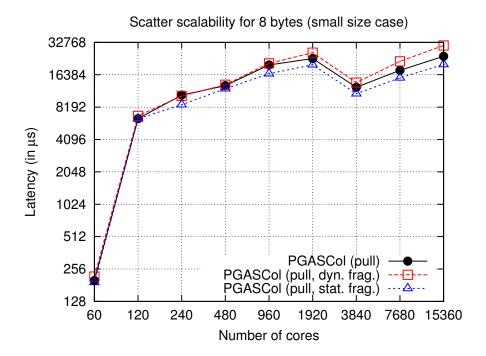

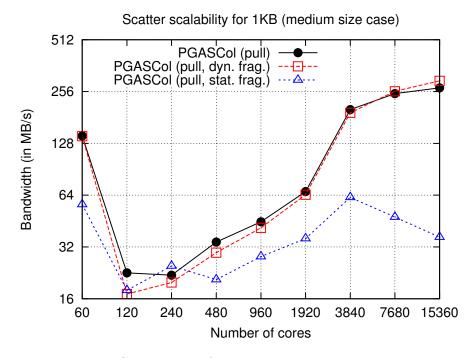

| 6.3.  | UPC scatter performance and scalability on Xeon Phi                                   |

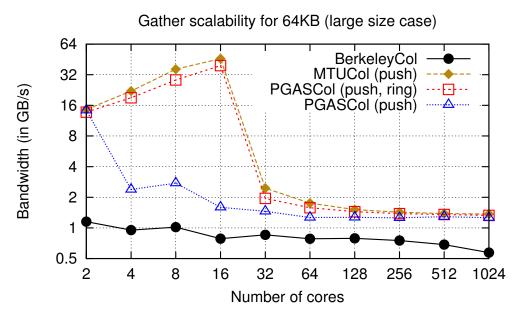

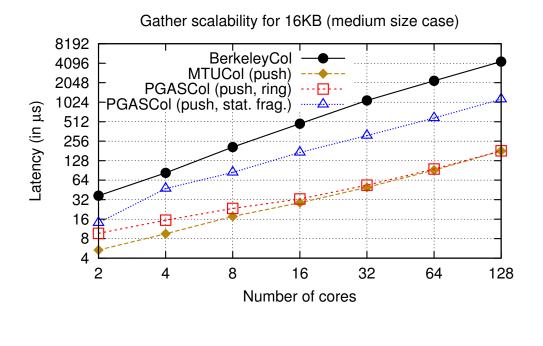

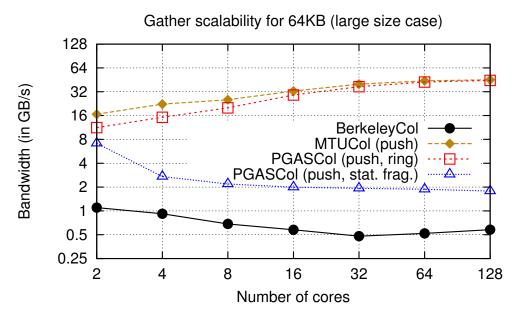

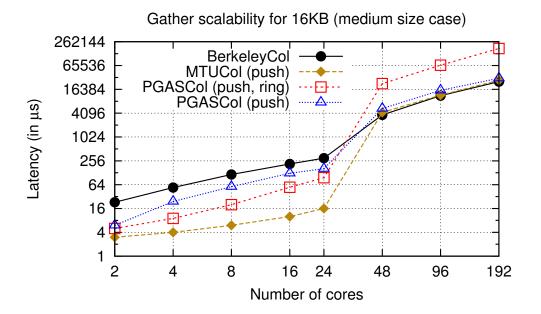

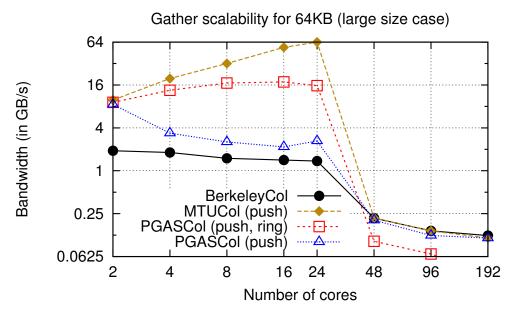

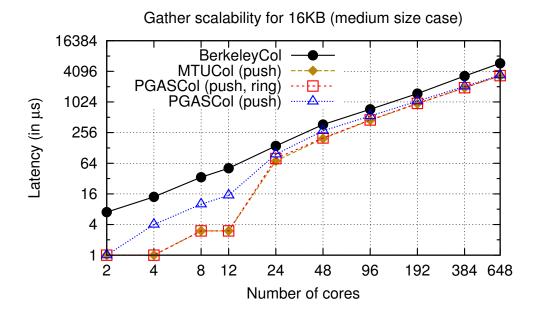

| 6.4.  | UPC gather performance and scalability on Xeon Phi                                    |

| 6.5.  | MPI broadcast performance and scalability on Xeon Phi $\ .\ .\ .\ .\ .$ . 135         |

| 6.6.  | MPI scatter performance and scalability on Xeon Phi                                   |

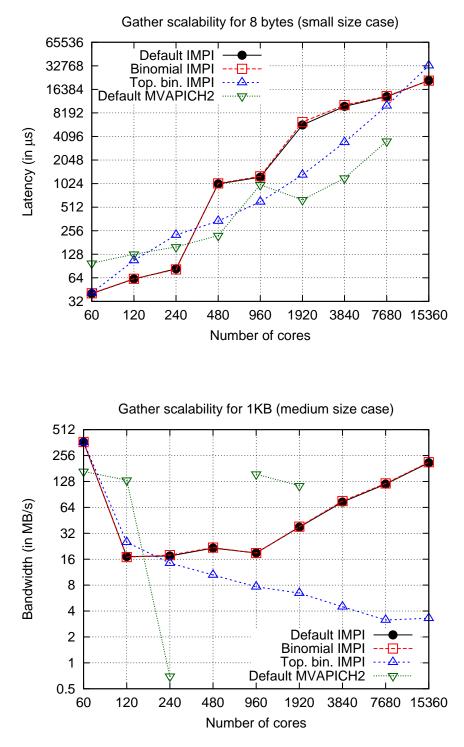

| 6.7. MPI gather performance and scalability on Xeon Phi                                                      |

|--------------------------------------------------------------------------------------------------------------|

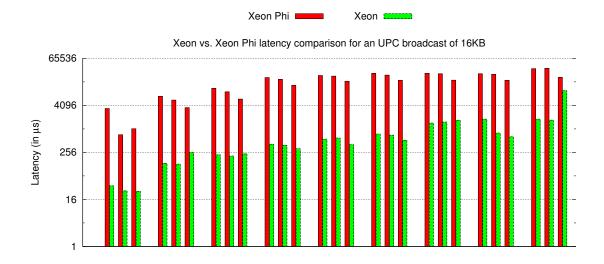

| 6.8. Performance comparison of UPC broadcast algorithms, for Xeon and Xeon Phi                               |

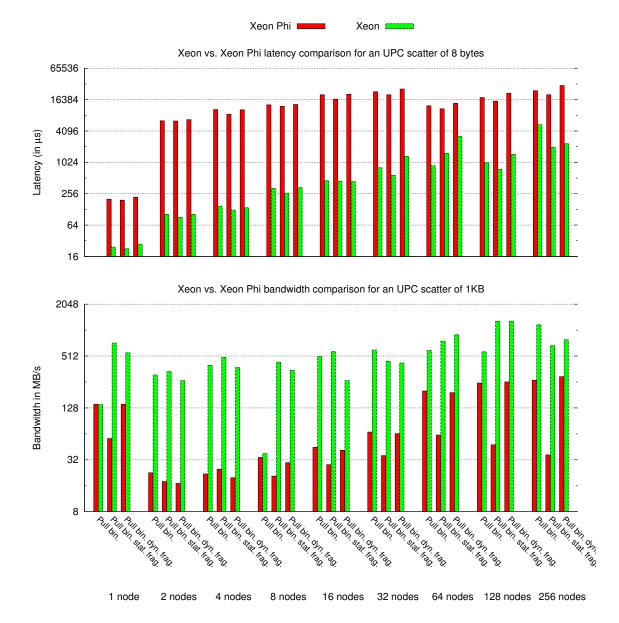

| 6.9. Performance comparison of UPC scatter algorithms, for Xeon and Xeon Phi                                 |

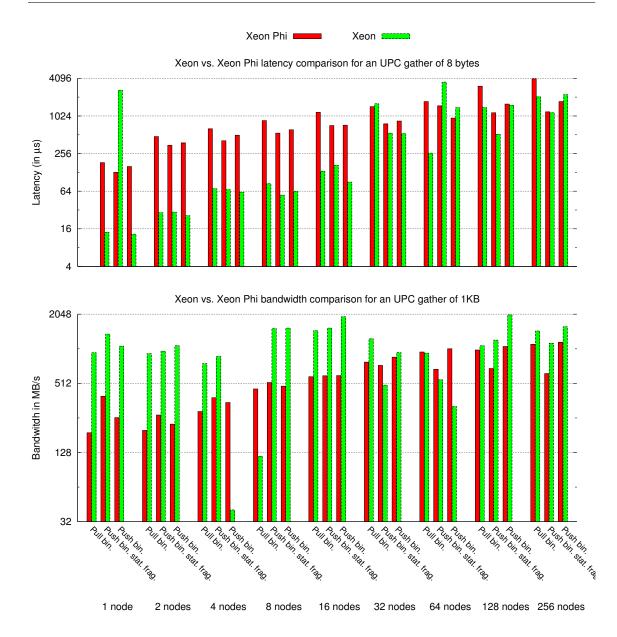

| 6.10. Performance comparison of UPC gather algorithms, for Xeon and Xeon Phi                                 |

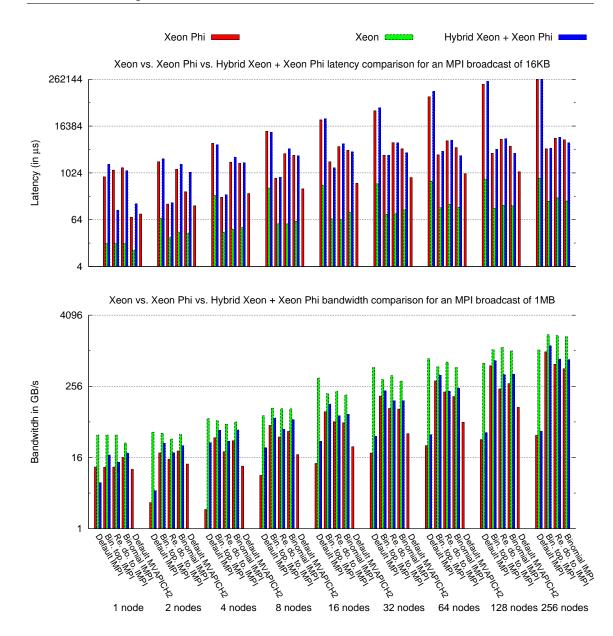

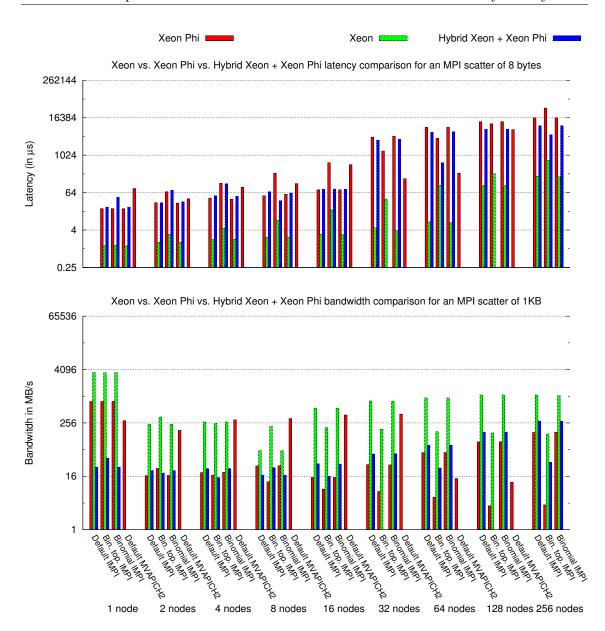

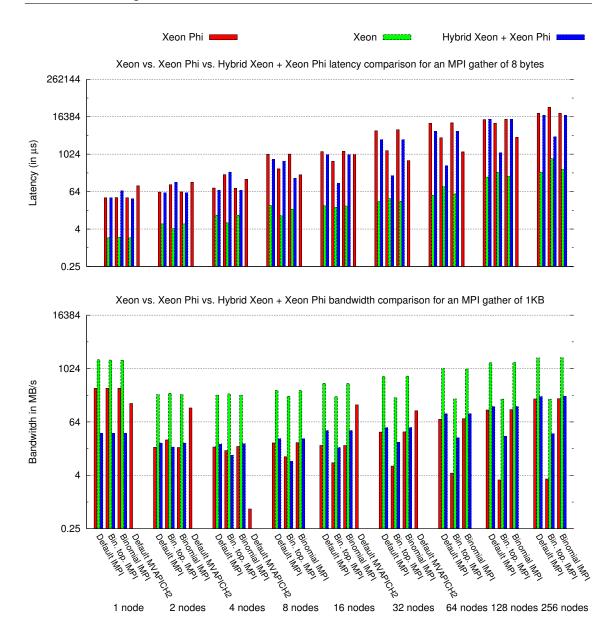

| 6.11. Performance comparison of MPI broadcast algorithms, for Xeon, Xeon<br>Phi and hybrid Xeon + Xeon Phi   |

| 6.12. Performance comparison of MPI scatter algorithms, for Xeon, Xeon<br>Phi and hybrid Xeon + Xeon Phi     |

| 6.13. Performance comparison of MPI gather algorithms, for Xeon, Xeon<br>Phi and hybrid Xeon + Xeon Phi      |

| 6.14. Performance comparison of MPI and UPC broadcast algorithms, for<br>Xeon Phi                            |

| 6.15. Performance comparison of MPI and UPC scatter algorithms, for<br>Xeon Phi                              |

| 6.16. Performance comparison of MPI and UPC gather algorithms, for<br>Xeon Phi                               |

| 6.17. Impact of number of pthreads per process on UPC broadcast perfor-<br>mance and scalability on Xeon Phi |

## Preface

Processor manufacturing hit the power wall nearly 10 years ago. As a result the microprocessor industry was forced to embrace a new era where the performance for new generation microprocessors came mainly from exposing more parallelism, rather than increased frequency. This posed a major shift in the industry, whose consequences are still difficult to deal with today. As a result current computer systems are based on multicore chips, which are constantly increasing their number of cores. This scenario, and particularly the new multicore processor architectures, heightens the importance of memory performance and scalability. The inclusion of the memory controller inside the processor's chip helps to minimize the issues associated with the access to shared memory from multicore chips. As a result, currently most systems, both single socket and multi-socket, have Non Uniform Memory Access (NUMA) architectures, as now processors package several memory controllers in a single chip. NUMA architectures provide scalability through the replication of paths to main memory, reducing the memory bus congestion as long as the accesses are evenly distributed among all the memory modules. This scalability is key for applications running on thousands of cores. The supercomputing community is now hitting a new power wall, where the power budget for supercomputers cannot grow anymore. As a result new creative ways are needed to circumvent this limitation. New approaches propose using small low-power processors like the ones used in cell phones (ARM) [92], with promising results. However, nowadays solutions rely in powerhungry manycore microarchitectures, such as Graphic Processing Units (GPUs) or Many Integrated Core (MICs) coprocessors, but with a good MFLOPS/Watt ratio. The emergence of these manycore devices has caused major changes in the HPC community. It has introduced a new level of complexity that the application developers have to deal with, adapting their applications to the new hardware, the new

levels of memory hierarchy present in the new processors, and the new APIs.

As a result of this ever increasing complexity, the HPC community has proposed new ways to program current systems. In the last few years a new programming model, Partitioned Global Address Space (PGAS), is becoming more popular. Despite not having the relevance of MPI, different important research groups are focusing on PGAS languages due to their potential [20]. One of their main features, one-sided asynchronous memory copies, has been already adopted in MPI. This feature can have an important role in the design of the ever important collective operations in scenarios with thousands of cores, where synchronizations becomes especially costly. Given this confluence of factors –complex hardware architectures with deeper memory hierarchies, new programming models and the importance to have efficient and scalable collective operations– this Thesis has designed, implemented and evaluated a set of collective operations in Unified Parallel C (UPC) –a PGAS language–.

Evaluation of performance is a central task in the development of HPC libraries of any kind. However, focusing on collectives for UPC, there is a lack of tools to assess methodically the performance of these libraries. As a prerequisite for the design and implementation of highly scalable collective algorithms, such a tool has been developed as part of this work, constituting one of the major contributions of this Thesis, as it provides a reference tool, equivalent to the Intel MPI Benchmarks for MPI runtimes.

The contents of this Ph.D. Thesis are organized as follows:

- Chapter 1, Background and State-of-the-art in Collective Operations provides the reader with an insightful explanation of the issues of programming modern high performance computing hardware, and how this affects the programming models used in this field. It continues with a description of the PGAS programming model, and an introduction of UPC as a popular PGAS language. Lastly, it provides a complete explanation of the state-of-the-art algorithms for collective operations.

- Chapter 2, *Characterization of UPC Performance* analyzes the performance of UPC in popular benchmarks, assessing its suitability for high performance

computing and postulating it as a candidate for the programming of current and future systems.

- Chapter 3, UPC Operations Microbenchmarking Suite: UOMS describes the design and implementation of the first microbenchmarking suite for UPC, explaining all the benchmarks included in the suite and various options available.

- Chapter 4, *Design of Scalable PGAS Collective Algorithms* details the design of the proposed PGAS collectives, and all the optimizations implemented in them. However, introductorily, it describes the existing collectives in UPC. Given that not all the operations distribute data equally, implementation details are discussed, with particular emphasis on collectives that fit tree structures.

- Chapter 5, *Perf. Evaluation of PGAS Collectives on NUMA Systems* analyzes the performance of the proposed algorithms for broadcast, reduce, scatter and gather in 5 different NUMA architectures. Comparisons with the reference implementation, and with the state-of-the-art collective library in UPC have been made. Additionally, the performance of a leading MPI implementation is compared with the performance of the proposed algorithms, and the impact of the different optimizations has been assessed and explained here.

- Chapter 6, *Perf. Evaluation of PGAS Collectives on Manycore Systems* analyzes the performance of the proposed algorithms for broadcast, scatter and gather in a manycore system, paying special attention to how they compare with the best of class algorithms for MPI for this platform, including manycore-optimized MPI runtimes.

- *Conclusions and Future Work* closes this Thesis, summarizing the conclusions and describing future lines of work.

Additionally, the user manual of the UPC Operations Microbenchmarking Suite is included as an appendix.

## Chapter 1

# Background and State-of-the-art in Collective Operations

The hardware used in current supercomputers has been following a trend since it hit the power wall, where the increase in performance came from exposing more parallelism –i.e. implementing multicore chips– instead of developing larger cores with higher clock speeds [49]. This poses a significant change, since now applications do not get a performance boost just by simply replacing the processor. Now parallelism at various levels becomes indispensable to achieve performance. In order to help programmers to cope with this new challenge, different programming models have been proposed. These new programming models open the opportunity to develop algorithms in more expressive ways. Collective operations, traditionally a key part of message-passing software, due to its convenience and optimized algorithms, can benefit from some of the features proposed by these new programming models.

This Chapter briefly discusses the most relevant programming models for High Performance Computing (HPC) in Section 1.1. Sections 1.2 and 1.3 complement the previous Section providing an overview of the Parallel Global Address Space (PGAS) programming model and its incarnations, as well as an introduction to Unified Parallel C (UPC). Section 1.4 provides a deep explanation of current stateof-the-art collective algorithms. Finally, Section 1.5 concludes the Chapter and discusses how PGAS features bring new opportunities for optimization of collective operations.

### 1.1. Programming Models

In the current multipetascale era, the discussion about programming models is becoming increasingly important. The complex modern hardware architectures require the use of multiple levels of paralellization. For internode parallelization, the message-passing is the most widely used parallel programming model as it is portable, scalable and provides good performance for a wide variety of computing platforms and codes. As the programmer has to manage explicitly data placement through point-to-point or collective operations, the programming of message passing software is difficult. MPI is the standard interface for message-passing libraries and there is a wide range of MPI implementations, both from HPC vendors and the free software community, optimized for high-speed networks, such as InfiniBand or Myrinet. MPI, although is oriented towards distributed memory environments, faces the raise of the number of cores per system with the development of efficient shared memory transfers and providing thread safety support.

For the intranode parallelization OpenMP is the most widely used solution, as it allows an easy development of parallel applications through compiler directives, that mainly distribute the work to be done between a number of threads. Moreover, it is becoming more important as the number of cores per system increases. However, as this model is limited to shared memory architectures, the performance is bound to the computational power of a single system. To avoid this limitation, hybrid systems, with both shared/distributed memory, such as multicore clusters, can be programmed using MPI+OpenMP. However, this hybrid model can make the parallelization more difficult and the performance gains could not compensate for the effort [89, 90]. In the last incarnation of OpenMP [83] -4.0 heavily influenced by OmpSs [17]- the concept of tasks becomes more important, as dependencies between tasks can be specified, allowing the runtime to create a graph that exposes more parallelism and hence increase efficiency of multi- and manycore systems.

In the last years, modern HPC systems have incorporated accelerators to boost computational power. This has introduced yet another level of complexity that requires programmers to deal with another programming model. This way, CUDA [74] (for NVIDIA accelerators) and OpenCL [99] (for NVIDIA and AMD accelerators) implement programming models focused on the efficient exploitation of accelerators with massive amounts of concurrent threads. Intel has also released their MIC – Many Integrated Core– architecture [41], based on x86 processors, that incorporates up to 61 cores in a coprocessor with very wide vector units, whose target is to provide a significant performance boost without requiring a complete rewriting of the applications.

The PGAS programming model combines some of the main features of the message-passing and the shared memory programming models. In PGAS languages, each thread has its own private memory space, as well as an associated shared memory region of the global address space that can be accessed by other threads, although at a higher cost than a local access. Thus, PGAS languages allow shared memory-like programming on distributed memory systems. Moreover, as in message-passing, PGAS languages allow the exploitation of data locality as the shared memory is partitioned among the threads in regions, each one with affinity to the corresponding thread.

### 1.2. PGAS Programming Model

The PGAS programming model has its origins in the appearance of the SHMEM (Symmetric Hierarchical Memory) [3] and Global Arrays libraries [75, 76, 85], around 1994. SHMEM is a family of libraries initially developed by Cray for its T3D supercomputer, that provides a shared-memory-like API to access memory in distributed memory systems. Likewise, Global Arrays is a toolkit developed by Pacific Northwest National Laboratory, that also provides a shared-memory-like API, and was developed with portability and efficiency in mind.

Acknowledging the potential of these libraries, a series of extensions were proposed to popular languages, in order to provide PGAS features to them. This way, Co-Array Fortran (CAF) [79, 80] is based on Fortran 95, adding PGAS support to it. CAF was included in the Fortran 2008 standard, becoming now an important part of the Fortran language. Unified Parallel C (UPC) [114] is based in C99, and adds support for declaring shared variables among UPC threads, as well as its distribution. It also provides a set of libraries. Titanium [121] is a PGAS extension to Java, whose code normally is compiled to native code instead of the byte code that runs in Java Virtual Machines.

Besides these extensions, the Defense Advanced Research Projects Agency (DARPA) of the United States of America developed the High Productivity Computing Systems (HPCS) programme, resulting in funding for the development of high productivity parallel languages. Each of these languages have been designed from scratch, incorporate PGAS features, and has been developed by a different vendor. X10 [10, 36] is an object oriented language developed by IBM, with two levels of concurrency, one for shared memory environments and another one for distributed memory, mapping accordingly to a cluster architecture. Chapel [7, 13] has been developed by Cray, with data and task parallelization as the main focus. Fortress [84, 98] is the Sun Microsystems (now Oracle) proposal for the HPCS, with implicit parallel features and advanced mathematical notation.

In the last few years, the library approach to PGAS has been also materialized basically in two libraries. OpenSHMEM [9] is the standard promoted after SHMEM, to ensure portability and avoid vendor lock in. Global Address Space Programming Interface (GASPI) [23] is another promising library, that allows to define different memory segments and provides advanced PGAS features.

Despite their differences, all these PGAS languages and libraries provide the programmer with the possibility of accessing remote memory directly, without intervention of the process whose memory is being accessed.

#### **1.3.** Introduction to UPC

UPC is the PGAS extension to the ISO C99 language, and has been used in this evaluation due to its important support by academia and industry. UPC provides PGAS features to C, allowing a more productive code development than other alternatives like MPI [19, 105]. Due to its programmability and performance –as well as being an extension of a popular programming language–, UPC has being in the focus of the research community for some time. There are commercial –IBM, Cray, HP– implementations, as well as more open initiatives –from the University of California Berkeley, Michigan Technological University, Intrepid/GCC, Ohio State University–, and optimized runtimes are available for all the major –and some minor, like the Tile64 processor [96]– platforms [35, 51, 56]. Recently, even GPU support was proposed and implemented [11], underlying the importance of UPC. However, as an emerging programming model, performance analysis are needed [6, 18, 22].

In the memory model defined by UPC, there are two very well differentiated regions: private and shared. The private region of a UPC thread is the same as a private region of a process. That is, belongs exclusively to that UPC thread, and no other UPC thread can directly access it. The shared region is the memory part that is readable and writeable by all the UPC threads in the job. However, this shared memory is divided in blocks, each of which has affinity –hence faster access– to one UPC thread.

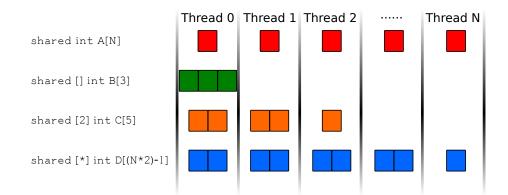

The programmer can define any kind of variable to be either private –by default– or shared, using the **shared** qualifier. In the case of defining shared arrays, the programmer can specify the blocking factor. I.e.: How many contiguous elements of the array belong to each thread. There are 4 ways to specify the blocking factor:

- Avoiding the use of the blocking factor: shared int A[N]. Implies a distribution with a block factor of 1.

- Using an empty blocking factor: shared [] int A[N]. Implies that the array is stored completely in the shared memory with affinity to the thread 0, i.e. a blocking factor of N.

- Using an explicit blocking factor: shared [2] int A[N]. Implies that the block factor is 2, i.e.: any given thread will hold in its shared memory 2 consecutive elements of the array.

- Using an automatic blocking factor: shared [\*] int A[N]. In this case the runtime will determine the blocking factor, trying to use a blocking factor as big as possible, a fair distribution among threads but without allocating more than one block per thread. I.e. a blocking factor of [(N + THREADS 1)/THREADS].

Figure 1.1 illustrates how the different blocking factors affect the distribution of arrays in UPC.

Figure 1.1: Distribution of arrays in shared memory in UPC

Memory, as in C, can be accessed with pointers. However, the addition of the shared memory space creates 4 possible situations:

- Private pointer to private memory. These are the regular C pointers.

- Private pointer to shared memory. These pointers allow UPC threads to keep references to shared memory in their private memory.

- Shared pointer to private memory. These pointers should be avoided. The pointers to private memory regions should not be allocated in the shared region, as it can lead to wrong memory accesses, due to potentially different private memory addresses of each variable.

- Shared pointer to shared memory. These pointers allow to share references to shared memory regions among different UPC threads.

Access to shared memory can be done just by referencing the desired variable, regardless of which threads owns that particular variable. However, there are a set of memory operations provided in order to perform copies of multiple elements at once. UPC initially provided upc\_memcpy, upc\_memget and upc\_memput. upc\_memcpy copies data from one shared memory location to another shared memory location. upc\_memget and upc\_memput operate similarly, but copying data from/to shared memory into/from private memory. This allows implicit parallelism and overlapping when distributing data, as multiple operations can be initiated simultaneously, one from each thread. This is of upmost importance in the design of PGAS collective

operations, as explained in Chapter 4, resulting in two variants: Pull and push, depending on the nature of the collective.

In the last UPC specification, 1.3 [115, 116, 117], there are also the non-blocking variants of these operations. The non-blocking variants have been proposed by the University of California Berkeley, and have been implemented in Berkeley UPC [51] before the last UPC specification.

The one-sided memory operations provided by UPC are a natural way of moving data in this language. Due to its asynchronicity, were UPC threads involved –source and destination– do not need to agree in establishing a communication, they are a powerful foundation for the implementation of collective operations.

### **1.4.** Collective Operations

The optimization of middleware for HPC is a complex task. It might involve all the layers of the runtime, and it should evolve with new versions of the language and library APIs [42, 122]. Within the runtime optimization, one of the most important points is the optimization of the collective operations, as most applications rely on them, both for programmability, as they implement popular operations, relieving the programmer from its error prone implementation, and also for performance, as they generally implement optimized and refined algorithms. Collective operations are usually key to achieve a good scalability. There are basically two approaches for the optimization of collective operations: the algorithmic and the system approach.

The algorithmic approach focuses on how the data is transferred and how the processes are organized. Not all algorithms can be suitable or implemented for all systems. Previous works on this field can be split between two main groups: distributed memory algorithms and shared memory algorithms, which target the main current architectures.

Kandalla et al. [46] developed and tested a topology-aware algorithm that builds the interconnect tree on InfiniBand clusters taking into account the process placement in relation to the switches, avoiding unnecessary switch hops. Similarly, Gong et al. developed an algorithm for MPI collectives in the cloud [28]. Bibo Tu et al.

[113] described a new broadcast algorithm for multicore clusters. In this algorithm two sets of communicators were used. The first one for intranode communications, where binding is used to improve locality within a node. The second one is for internode communications. This way a broadcast is performed in two steps, interand intranode transfer steps, avoiding the network interface congestion. Kumar et al. [50] designed and evaluated an all-to-all algorithm for multicore clusters. This algorithm is similar to the Bibo Tu's broadcast algorithm, in the sense that is performed in two steps. Chan et al. [8] proposed an algorithm that takes advantage of architectures with multiple links, where messages can be sent simultaneously over different links in systems with N-dimensional meshes/tori. Kandalla et al. [47] also proposed a design for broadcast, reduce and all reduce operations on symmetric scenarios on Xeon Phi. Their design minimizes the use of the PCIe bus and always uses a process on the main processor to communicate with remote nodes. This is the only design specifically targeting Xeon Phi coprocessors. However, it is just valid for hybrid scenarios, involving both Xeon Phi and main processors, and can not be applied to native scenarios (Xeon Phi only), where there are not main processors involved. To solve that Potluri et al. [86] proposed the use of an proxy service running on the main processor, even if the main processor is not used in the job. Intel followed a similar approach with their Coprocessor Communication Link proxy (CCL-proxy) for Intel MPI.

Other works have focused on optimizations for shared memory. Nishtala et al. [77] conducted a series of experiments in three shared memory systems, based on multicore processors, using k-nomial trees for representing the virtual topology of the processes. These experiments demonstrated that for each architecture and message size the optimal radix of the k-nomial trees is different. Graham et al. [33] designed and tested a series of algorithms for shared memory, each one appropriate for a set of functions and message sizes. The described algorithms are basically fan-in or fan-out trees of variable radix; reduce-scatter (each process reduces its data) followed by a gather or all-gather; and a recursive doubling algorithm. Ramos et al. [94] modelled collective communications for cache coherent systems, and proposed enhancements for Xeon Phi taking into account the specific details of its cache implementation. As expected, every algorithm is the best performer for some setups, whereas not optimal for others.

Additionally, there are some works that aimed to optimize both shared and distributed memory architectures, such as the work of Mamidala et al. [65], which implements and evaluates similar algorithms to the previous works. A work closer to the work done on this Thesis is the multi-leader algorithm proposed by Kandalla et al. [45]. This proposal is similar to Bibo Tu's broadcast algorithm, except for using more than one leader per node, initially considering only the allgather operation. Nishtala et al. [78] leveraged shared memory and trees to optimize collectives and explore their autotuning possibilities. Qian [88] followed a similar path to Kandalla et al. and proposed a series of algorithms mainly focused on all-to-all and allgather, targeting multicore systems with multiple connections per node, as well as optimizing the algorithms for cases where different processes arrive at the collective at a different time.

The algorithms considered in the related work are usually independent of their actual implementation in a particular language. However, they have been generally developed using MPI or UPC. Usually there is no algorithm that always outperforms the others. In fact, the performance of an algorithm depends on three factors: (1) message size, (2) number of processes involved, and (3) the hardware, including the network topology. Providing the best algorithm for each setup and message size is the optimum approach, as demonstrated in [106]. However, selecting among the algorithms entails a significant effort, as they are highly dependent on the system. The solution typically relies on autotuning [118], generally based on an automatic performance characterization of each algorithm for a wide range of setups.

Furthermore, it is possible to adapt the runtimes to the underlying hardware. This typically rely on adding software features in order to achieve a better usage of the hardware, or adapting hardware specific layers to a given architecture, e.g., the network layer. Miao et al. [69] proposed a single copy method to take advantage of shared memory architectures, avoiding the system buffer. The proposal of Trahay et al. relies on a multithreaded communication engine to offload small messages [112]. Brightwell et al. [4] propose the sharing of page tables between processes, speeding up applications performance. Hoefler et al. [34] proposed the use of multicast in networks, resulting in highly scalable operations, but just valid for very small messages. Velamati et al. [119] designed a set of algorithms for MPI collective operations for the heterogeneous Cell processor. More recently, Li et al. [53]

have proposed a NUMA-aware multithreaded MPI runtime, where MPI ranks are implemented as threads as opposed to processes, and they have implemented and evaluated algorithms for allreduce in this runtime. Regarding experiences with Xeon Phi and UPC, Luo et al. [57] performed the first general performance evaluation of UPC and MPI on Xeon Phi, slightly covering point to point and collective communication performance, and computational kernels. Potluri et al. [87] optimized MVAPICH2 for Xeon Phi by leveraging the Symmetric Communications InterFace (SCIF), a low level API that allows to control the DMA engines.

The work done up to now successfully adapted collectives to different architectures. However, it does not combine one-sided communications –so common in PGAS languages–, pipelining/overlapping and hierarchical trees. New NUMA architectures and manycore coprocessors with direct access to the network can benefit from these features.

### 1.5. Conclusions of Chapter 1

The scientific community have seen a growing number of programming models in the last years. Some of them address the complexity of process communication in distributed memory systems, incorporating new features. PGAS, with its inherent easiness for remote memory access, is the most promising alternative to traditional message-passing.

Research on collective operations has been an ongoing topic for computer scientist working on optimization of parallel runtimes for a number of years. Typically, changes in the underlying hardware opened a door to new optimizations to better utilize the system resources. Now, with the blooming potential of UPC, a new door has been opened to develop new algorithms that efficiently exploit one-sided remote memory accesses and that are aware of the substantial changes that are taking place in processors architectures.

The next Chapter of this Thesis will characterize the performance of UPC, as a representative PGAS language, to assess its suitability as a language for HPC, and as an alternative to MPI. Most current systems are NUMA clusters, which motivates this characterization to be focused in such architectures.

## Chapter 2

# Characterization of UPC Performance

The PGAS paradigm has been proposed as a programming model with substantial benefits over more traditional models such as message-passing. The distributed shared memory and one-sided memory copies make it an attractive alternative for scientific computing, where programmers typically are more focused on their field of study than on explicitly managing low-level functions. However, without efficient compilers and runtimes that can extract significant performance out of the hardware they are running on, PGAS alternatives such as UPC cannot be considered as a viable approach for future HPC. Nevertheless, the value of the PGAS approach has been already validated. The PGAS extension to Fortran –Co-Array Fortran–, equivalent to UPC for the C language, has been used successfully [72], reaching goals that are not attainable by traditional message-passing and underlining the potential of the PGAS approach. Given the focus on UPC of this Thesis, this Chapter analyzes the behavior of UPC, comparatively with MPI. For this, the most important benchmarks have been used. Section 2.1 explains the benchmarks and analyzes the benchmark results. Section 2.2 exposes additional UPC performance analyses, done by other researchers. Section 2.3 summarizes the conclusions of the Chapter.

### 2.1. Representative Benchmarks for UPC Performance Characterization

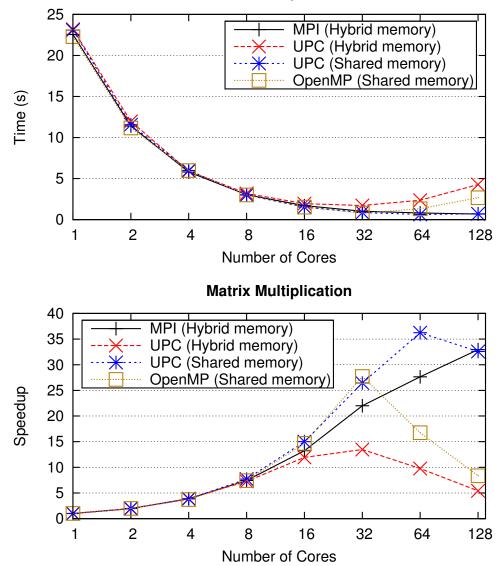

The number of benchmarks available that support the direct comparison of UPC and MPI is quite reduced. One of this benchmarks is the de-facto standard for benchmarking HPC systems, the NAS Parallel Benchmarks [2, 73]. Due to its importance and availability they have been used in a wide amount of performance comparisons [1, 43, 64, 93, 95]. Additionally, the NPB implemented in UPC have been already studied in the past, making comparisons between UPC, MPI and OpenMP. Jin et al. [44] developed in UPC their own implementation of the 3 pseudo application codes contained in the NPB –ST, BT and LU–, and compared then with a C implementation of the NPB, using MPI to communicate between processes. They have used the B class –a medium problem size– in 2 different systems. Their findings revealed a performance practically equivalent between the UPC and C+MPI implementations of the NPB. El-Ghazawi and Cantonnet [18] compared the performance of NPB-MPI -implemented in Fortran- with NPB-UPC on a 16 processor Compag AlphaServer SC cluster, using the class B workload. Cantonnet et al.[6] used two SGI Origin NUMA machines, each one with 32 processors, using the class A workload for 3 NPB kernels. El-Ghazawi et al. [21] compared MPI with UPC very briefly using 2 NPB kernels and class B, in a Cray X1 machine. However, none of these comparisons accounted for modern NUMA hardware using large workloads -class C- as does Subsection 2.1.1. Besides the NPB, matrix multiplication and stencil-like computations are two typical computational kernels widely extended in many scientific applications. Therefore Subsection 2.1.2, assesses the scalability of matrix multiplication kernels in distributed memory paradigms, and a Sobel edge detector.

The testbed used in this analysis is the Finis Terrae supercomputer [107], composed of 142 HP Integrity rx7640 nodes, each one with 8 Montvale Itanium 2 dualcore processors (16 cores per node) at 1.6 GHz and 128 GB of memory, interconnected via InfiniBand. The InfiniBand HCA is a dual 4X IB port (16 Gbps of theoretical effective bandwidth). For the evaluation of the hybrid shared/distributed memory scenario, 8 nodes have been used (up to 128 cores). The number of cores used per node in the performance evaluation is  $\lceil n/8 \rceil$ , being *n* the total number of cores used in the execution, with consecutive distribution. An HP Integrity Superdome system with 64 Montvale Itanium 2 dual-core processors (total 128 cores) at 1.6 GHz and 1 TB of memory has also been used for the shared memory evaluation. The nodes were used without other users processes running, and the process affinity was handled by the operating system scheduler.

The MPI library is the recommended by the hardware vendor, HP MPI 2.2.5.1 using InfiniBand Verbs (IBV) for internode communication, and shared memory transfers (HP MPI SHM driver) for intranode communication. The UPC compiler is Berkeley UPC 2.8, which uses the IBV driver for distributed memory communication, and POSIX threads (from now on pthreads) within a node for shared memory transfers. The backend for both and OpenMP compiler is the Intel 11.0.069.

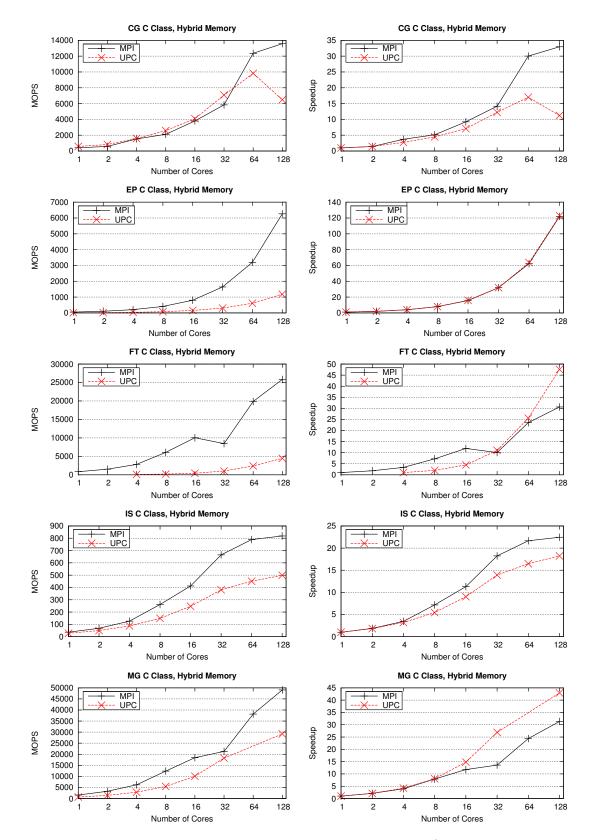

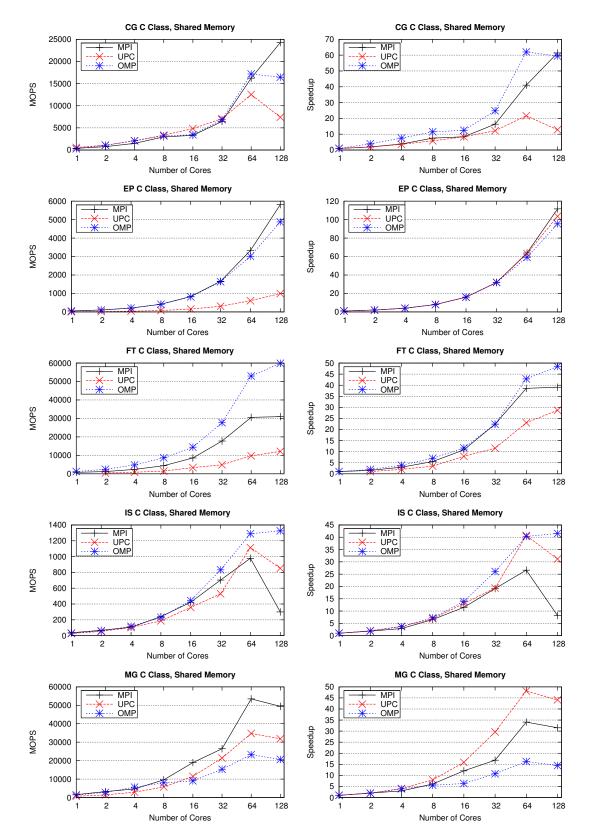

#### 2.1.1. NAS Parallel Benchmarks (NPB)

The NPB consist of a set of kernels and pseudo-applications, taken primarily from Computational Fluid Dynamics (CFD) applications. These benchmarks reflect different kinds of computation and communication patterns that are important across a wide range of applications, which makes them the de facto standard in parallel performance benchmarking. There are NPB implementations available for a wide range of parallel programming languages and libraries, such as MPI (from now on NPB-MPI), UPC (from now on NPB-UPC), OpenMP (from now on NPB-OMP), a hybrid MPI+OpenMP implementation (not used in this comparative evaluation as it implements benchmarks not available in NPB-UPC), HPF and Message-Passing Java [64], among others. The most used subset of the NPB are the kernels Conjugate Gradient (CG), Embarrassingly Parallel (EP), Fourier Transform (FT), Integer Sort (IS) and Multi Grid (MG). All these kernels use double precision, except IS, that operates with integer data. Additionally, the original NPB specification also contained three pseudo-applications: Block Tridiagonal solver (BT), Scalar Pentadiagonal solver (SP) and Lower-Upper Gauss-Seidel solver (LU). For all these benchmarks there are different sizes defined, ranging from class A – the smaller– to class E.